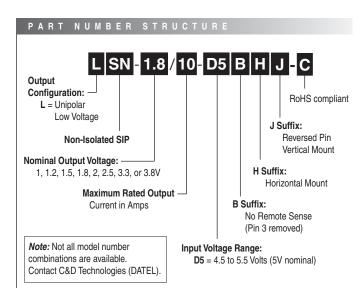

# Single Output LSN-10A D5 Models

Non-Isolated, 5VIN, 1-3.8VOUT 10 Amp DC/DC's in SIP Packages

#### **Features**

- Industry-standard SIP pinout

- Shorter (2.0" vs. 2.5") package length

- 4.5-5.5V input range

- 1/1.2/1.5/1.8/2/2.5/3.3/3.8Vout @ 10A

- Non-isolated, fully synchronous, 300kHz, buck topology

- Outstanding performance:

- ±1% setpoint accuracy

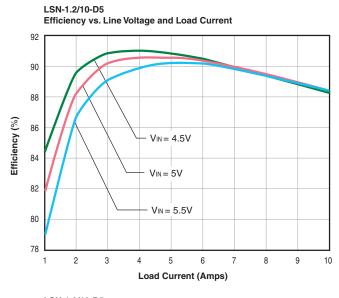

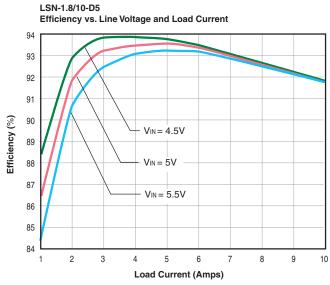

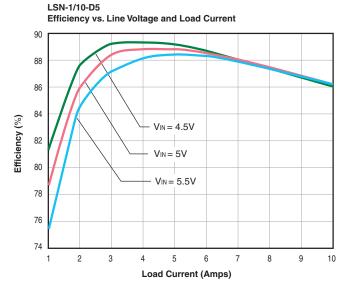

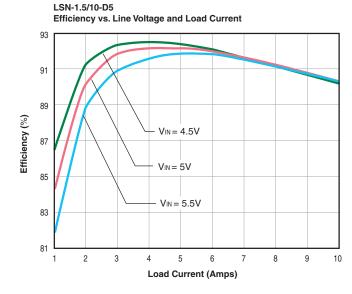

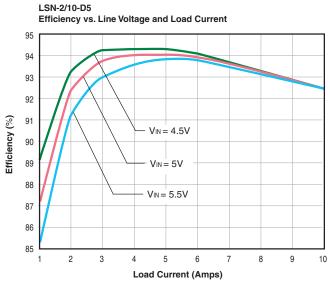

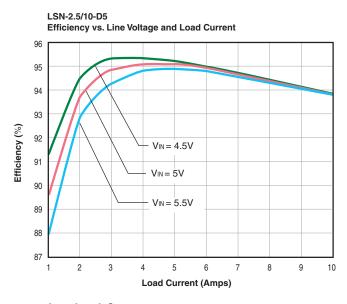

- Efficiencies to 95% @ 10 Amps

- · Noise as low as 10mVp-p

- · Stable no-load operation

- Trimmable output voltage

- Remote on/off and sense pins

- Thermal shutdown

- No derating to +71°C, natural convection

- UL/IEC/EN60950 certified

- EMC compliant

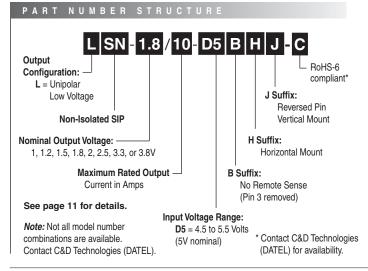

C&D's new LSN D5 Series SIP's (single-in-line packages) are non-isolated DC/DC converters that accept a 5V input (4.5V to 5.5V input range) and deliver 1V, 1.2V, 1.5V, 1.8V, 2V, 2.5, 3.3 or 3.8V outputs at 10 Amps. LSN D5 SIP's take on-board 5V power and convert it, with the highest efficiency in the smallest space, to any lower voltage required by today's current-hungry DSP's, ASIC's and CPLD's.

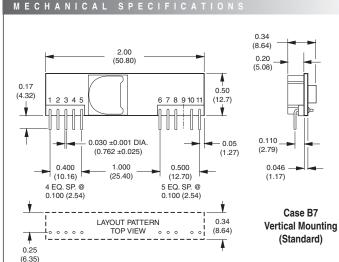

The miniature size of LSN D5's makes them ideal for true point-of-use power processing. Vertical-mount packages occupy a mere 0.7 square inches (440 sq. mm), and they are available in industry-standard and Tyco-compatible pinout. Horizontal-mount packages ("H" suffix) are only 0.34 inches (8.6mm) high.

The LSN's best-in-class power density is achieved with a fully synchronous, fixed-frequency (300kHz), buck topology that also delivers: high efficiency (to 95%), low noise (10mVp-p typ.), tight line/load regulation ( $\pm 0.1\%/\pm 0.25\%$  max.), quick step response (100 $\mu$ sec), stable no-load operation, and no output reverse conduction.

The fully functional LSN's feature output overcurrent detection, continuous short-circuit protection, an output-voltage trim function, a remote on/off control pin (pull high to disable), thermal shutdown, and a sense pin. High efficiency enables the LSN D5's to deliver rated output currents of 10 Amps at ambient temperatures to +71°C with no air flow (natural convection).

If your low-voltage, high-current requirements make the use of inefficient linear regulators impractical, take a look at one of C&D's easy-to-use, low-cost LSN SIP's. All devices are UL/IEC/EN60950 certified and EMC compliant. UL, CB, HALT and EMC reports are available upon request. Selected models are RoHS compliant.

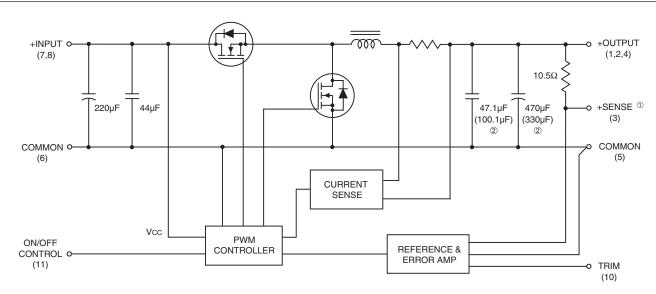

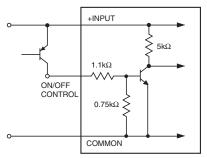

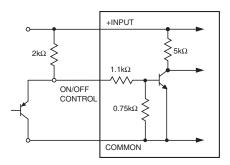

Figure 1. Simplified Schematic

① For devices with the sense-pin removed ("B" suffix), the feedback path is through the +Output pin and not the +Sense pin.

② Values in parenthesis for 3.3V models only.

Typical topology is shown.

#### Performance Specifications and Ordering Guide <sup>①</sup>

|                    | Output  |        |        |          |            | Input      |          |         | Efficiency |       |       | Daalrana |                   |

|--------------------|---------|--------|--------|----------|------------|------------|----------|---------|------------|-------|-------|----------|-------------------|

|                    | Vоит    | Іоит   | R/N (m | ıVp-p) ② | Regulation | າ (Max.) ③ | VIN Nom. | Range   | lin ④      | Full  | Load  | ½ Load   | Package<br>(Case, |

| Model <sup>©</sup> | (Volts) | (Amps) | Тур.   | Max.     | Line       | Load       | (Volts)  | (Volts) | (mA/A)     | Min.  | Тур.  | Тур.     | Pinout)           |

| LSN-1/10-D5        | 1       | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/2.43    | 83%   | 86%   | 89%      | B7/B7x, P59       |

| LSN-1.2/10-D5      | 1.2     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/2.85    | 85%   | 88%   | 91%      | B7/B7x, P59       |

| LSN-1.5/10-D5      | 1.5     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/3.48    | 87%   | 90%   | 92%      | B7/B7x, P59       |

| LSN-1.8/10-D5 ⑤    | 1.8     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/4.09    | 89%   | 91.5% | 93.5%    | B7/B7x, P59       |

| LSN-2/10-D5        | 2       | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/4.51    | 89.5% | 92.5% | 94%      | B7/B7x, P59       |

| LSN-2.5/10-D5      | 2.5     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/5.50    | 91%   | 94%   | 95.5%    | B7/B7x, P59       |

| LSN-3.3/10-D5      | 3.3     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/7.25    | 92%   | 95%   | 96%      | B7/B7x, P59       |

| LSN-3.8/10-D5      | 3.8     | 10     | 10     | 35       | ±0.1%      | ±0.25%     | 5        | 4.5-5.5 | 50/8.0     | 92%   | 95%   | 96%      | B7/B7x, P59       |

- ① Typical at TA = +25°C under nominal line voltage and full-load conditions, unless otherwise noted. All models are tested and specified with external 22µF input and output capacitors. These capacitors are necessary to accommodate our test equipment and may not be required to achieve specified performance in your applications. See I/O Filtering and Noise Reduction.

- ② Ripple/Noise (R/N) is tested/specified over a 20MHz bandwidth and may be reduced with external filtering. See I/O Filtering and Noise Reduction for details.

- 3 These devices have no minimum-load requirements and will regulate under no-load conditions. Regulation specifications describe the output-voltage deviation as the line voltage or load is varied from its nominal/midpoint value to either extreme.

- Mominal line voltage, no-load/full-load conditions.

- ⑤ Avaiilable with RoHS (Reduction of Hazardous Substances) compliance.

- 6 These are not complete model numbers. Please use the Part Number Structure when ordering.

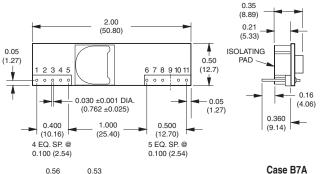

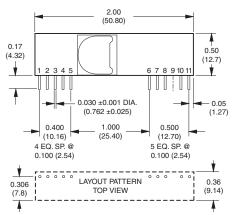

Dimensions in inches (mm)

| I/O Connections |               |     |               |     |                |  |  |

|-----------------|---------------|-----|---------------|-----|----------------|--|--|

| Pin             | Function P59* | Pin | Function P59* | Pin | Function P59*  |  |  |

| 1               | +Output       | 5   | Common        | 9   | No Pin         |  |  |

| 2               | +Output       | 6   | Common        | 10  | Vout Trim      |  |  |

| 3               | +Sense *      | 7   | +Input        | 11  | On/Off Control |  |  |

| 4               | +Output       | 8   | +Input        |     |                |  |  |

Reverse Pin

Vertical Mounting

(Tyco-compatible)

Pin 3 (+Sense) removed for "B" suffix models.

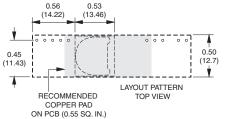

**Horizontal Mounting**

#### Performance/Functional Specifications

Typical @ T<sub>A</sub> = +25°C under nominal line voltage and full-load conditions unless noted. ①

|                                         | nput                                |  |  |  |

|-----------------------------------------|-------------------------------------|--|--|--|

| Input Voltage Range                     | 4.5 to 5.5 Volts (5V nominal)       |  |  |  |

| Input Current:                          |                                     |  |  |  |

| Normal Operating Conditions             | See Ordering Guide                  |  |  |  |

| Inrush Transient                        | 0.014A <sup>2</sup> sec             |  |  |  |

| Standby/Off Mode                        | 3mA                                 |  |  |  |

| Output Short-Circuit Condition ②        | 70mA average                        |  |  |  |

| Input Reflected Ripple Current ②        | 50mAp-p                             |  |  |  |

| Input Filter Type                       | Capacitive (264µF)                  |  |  |  |

| Overvoltage Protection                  | None                                |  |  |  |

| Reverse-Polarity Protection             | None                                |  |  |  |

| Undervoltage Shutdown                   | None                                |  |  |  |

| On/Off Control ② ③                      | On = open (internal pulldown)       |  |  |  |

|                                         | Off = $+2.8V$ to $+V$ IN ( $<3mA$ ) |  |  |  |

| 0                                       | utput                               |  |  |  |

| Vout Accuracy (50% load)                | ±1% maximum                         |  |  |  |

| Minimum Loading ①                       | No load                             |  |  |  |

| Maximum Capacitive Load                 | 10,000μF (electrolytic)             |  |  |  |

| Vouт Trim Range ②                       | ±10%                                |  |  |  |

| Ripple/Noise (20MHz BW) ① ② ④           | See Ordering Guide                  |  |  |  |

| Total Accurcacy                         | 3% over line/load/temperature       |  |  |  |

| Efficiency ②                            | See Ordering Guide                  |  |  |  |

| Overcurrent Detection and Short-Circ    | uit Protection: ②                   |  |  |  |

| Current-Limiting Detection Point        | 17 (12.5-22) Amps                   |  |  |  |

| Short-Circuit Detection Point           | 98% of Vou⊤ set                     |  |  |  |

| SC Protection Technique                 | Hiccup with auto recovery           |  |  |  |

| Short-Circuit Current                   | 400mA average                       |  |  |  |

| Dynamic C                               | Characteristics                     |  |  |  |

| Transient Response (50% load step)      | 50µsec to ±2% of final value        |  |  |  |

| Start-Up Time: ②                        |                                     |  |  |  |

| Vin to Vout                             | 7msec                               |  |  |  |

| On/Off to Vout                          | 6msec                               |  |  |  |

| Switching Frequency                     | 300kHz (+40kHz, -50kHz)             |  |  |  |

| <u>Envir</u>                            | onmental                            |  |  |  |

| MTBF: Bellcore, ground fixed, TA = +25° | CC,                                 |  |  |  |

| full power, natural convection,         | •                                   |  |  |  |

| +55°C component temperature             | 2.1 million hours                   |  |  |  |

| Operating Temperature: (Ambient) ②      |                                     |  |  |  |

| Without Derating (Natural convection)   | -40 to +63/71°C (model dependent)   |  |  |  |

| With Derating (Natural convection)      | See Derating Curves                 |  |  |  |

| Thermal Shutdown                        | +115°C                              |  |  |  |

|                                         |                                     |  |  |  |

|                                         | nysical                             |  |  |  |

| Dimensions                              | See Mechanical Specifications       |  |  |  |

| Package                                 | Open-frame, single-in-line (SIP)    |  |  |  |

| Pin Dimensions/Material                 | 0.03" (0.76mm) round copper with    |  |  |  |

① All models are tested/specified with external 22µF input/output capacitors. These caps accommodate our test equipment and may not be required to achieve specified performance in your applications. All models are stable and regulate within spec under no-load conditions.

gold plate over nickel underplate

UL/cUL/IEC/EN 60950, CSA-C22.2 No. 234

0.3 ounces (8.5g)

UL94V-0

② See Technical Notes and Performance Curves for details.

Weight

Safety

Flamability Rating

- The On/Off Control (pin 11) is designed to be driven with open-collector logic or the application of appropriate voltages (referenced to Common, pins 5 and 6).

- 4 Output noise may be further reduced with the installation of additional external output filtering. See I/O Filtering and Noise Reduction.

#### **Absolute Maximum Ratings**

Input Voltage:

Continuous or transient 7 Volts

On/Off Control (Pin 11) +VIN

Input Reverse-Polarity Protection None

Output Overvoltage Protection None

Output Current Current limited. Devices can

withstand sustained output short

circuits without damage.

Storage Temperature -40 to +125°C

Lead Temperature (soldering, 10 sec.) +300°C

These are stress ratings. Exposure of devices to any of these conditions may adversely affect long-term reliability. Proper operation under conditions other than those listed in the Performance/Functional Specifications Table is not implied.

#### TECHNICAL NOTES

#### **Return Current Paths**

The LSN D5 SIP's are non-isolated DC/DC converters. Their two Common pins (pins 5 and 6) are connected to each other internally (see Figure 1). To the extent possible (with the intent of minimizing ground loops), input return current should be directed through pin 6 (also referred to as –Input or Input Return), and output return current should be directed through pin 5 (also referred to as –Output or Output Return). Any on/off control signals applied to pin 11 (On/Off Control) should be referenced to Common (specifically pin 6).

#### I/O Filtering and Noise Reduction

All models in the LSN D5 Series are tested and specified with external 22µF input and output capacitors. These capacitors are necessary to accommodate our test equipment and may not be required to achieved desired performance in your application. The LSN D5's are designed with high-quality, high-performance *internal* I/O caps, and will operate within spec in most applications with *no additional external components*.

In particular, the LSN D5's input capacitors are specified for low ESR and are fully rated to handle the units' input ripple currents. Similarly, the internal output capacitors are specified for low ESR and full-range frequency response. As shown in the Performance Curves, removal of the external output caps has minimal effect on output noise.

In critical applications, input/output ripple/noise may be further reduced using filtering techniques, the simplest being the installation of external I/O caps.

External input capacitors serve primarily as energy-storage devices. They minimize high-frequency variations in input voltage (usually caused by IR drops in conductors leading to the DC/DC) as the switching converter draws pulses of current. Input capacitors should be selected for bulk capacitance (at appropriate frequencies), low ESR, and high rms-ripple-current ratings. The switching nature of modern DC/DC's requires that the dc input voltage source have low ac impedance at the frequencies of interest. Highly inductive source impedances can greatly affect system stability. Your specific system configuration may necessitate additional considerations.

Output ripple/noise (also referred to as periodic and random deviations or PARD) may be reduced below specified limits with the installation of additional external output capacitors. Output capacitors function as true filter

elements and should be selected for bulk capacitance, low ESR, and appropriate frequency response. Any scope measurements of PARD should be made directly at the DC/DC output pins with scope probe ground less than 0.5" in length.

All external capacitors should have appropriate voltage ratings and be located as close to the converters as possible. Temperature variations for all relevant parameters should be taken into consideration.

The most effective combination of external I/O capacitors will be a function of your line voltage and source impedance, as well as your particular load and layout conditions. Our Applications Engineers can recommend potential solutions and discuss the possibility of our modifying a given device's internal filtering to meet your specific requirements. Contact our Applications Engineering Group for additional details.

#### **Input Fusing**

Most applications and or safety agencies require the installation of fuses at the inputs of power conversion components. LSN D5 Series DC/DC converters are not internally fused. Therefore, if input fusing is mandatory, either a normal-blow or a slow-blow fuse with a value no greater than 15 Amps should be installed within the ungrounded input path to the converter.

As a rule of thumb however, we recommend to use a normal-blow or slowblow fuse with a typical value of about twice the maximum input current, calculated at low line with the converters minimum efficiency.

#### Safety Considerations

LSN D5 SIP's are non-isolated DC/DC converters. In general, all DC/DC's must be installed, including considerations for I/O voltages and spacing/ separation requirements, in compliance with relevant safety-agency specifications (usually UL/IEC/EN60950).

In particular, for a non-isolated converter's output voltage to meet SELV (safety extra low voltage) requirements, its input must be SELV compliant. If the output needs to be ELV (extra low voltage), the input must be ELV.

Input Overvoltage and Reverse-Polarity Protection

LSN D5 SIP Series DC/DC's do not incorporate either input overvoltage or input reverse-polarity protection. Input voltages in excess of the specified absolute maximum ratings and input polarity reversals of longer than "instantaneous" duration can cause permanent damage to these devices.

# Start-Up Time

The V<sub>IN</sub> to V<sub>OUT</sub> Start-Up Time is the interval between the time at which a ramping input voltage crosses the lower limit of the specified input voltage range (4.5 Volts) and the fully loaded output voltage enters and remains within its specified accuracy band. Actual measured times will vary with input source impedance, external input capacitance, and the slew rate and final value of the input voltage as it appears to the converter.

The On/Off to Vout Start-Up Time assumes the converter is turned off via the On/Off Control with the nominal input voltage already applied to the converter. The specification defines the interval between the time at which the converter is turned on and the fully loaded output voltage enters and remains within its specified accuracy band. See Typical Performance Curves.

#### **Remote Sense**

LSN D5 SIP Series DC/DC converters offer an output sense function on pin 3. The sense function enables point-of-use regulation for overcoming moderate

IR drops in conductors and/or cabling. Since these are non-isolated devices whose inputs and outputs usually share the same ground plane, sense is provided only for the +Output.

The remote sense line is part of the feedback control loop regulating the DC/DC converter's output. The sense line carries very little current and consequently requires a minimal cross-sectional-area conductor. As such, it is not a low-impedance point and must be treated with care in layout and cabling. Sense lines should be run adjacent to signals (preferably ground), and in cable and/or discrete-wiring applications, twisted-pair or similar techniques should be used. To prevent high frequency voltage differences between Vout and Sense, we recommend installation of a 1000pF capacitor close to the converter.

The sense function is capable of compensating for voltage drops between the +Output and +Sense pins that do not exceed 10% of  $V_{\text{OUT}}$ .

$$[Vout(+) - Common] - [Sense(+) - Common] \le 10\%Vout$$

Power derating (output current limiting) is based upon maximum output current and voltage at the converter's output pins. Use of trim and sense functions can cause the output voltage to increase, thereby increasing output power beyond the LSN's specified rating. Therefore:

(Vout at pins)

$$x$$

(lout)  $\leq$  rated output power

The internal  $10.5\Omega$  resistor between +Sense and +Output (see Figure 1) serves to protect the sense function by limiting the output current flowing through the sense line if the main output is disconnected. It also prevents output voltage runaway if the sense connection is disconnected.

Note: Connect the +Sense pin (pin 3) to +Output (pin 4) at the DC/DC converter pins, if the sense function is not used for remote regulation.

#### On/Off Control and Power-up Sequencing

The On/Off Control pin may be used for remote on/off operation. LSN D5 SIP Series DC/DC's are designed so they are enabled when the control pin is left open (internal pull-down to Common) and disabled when the control pin is pulled high  $(+2.8V \text{ to } + V_{IN})$ , as shown in Figure 2 and 2a.

Dynamic control of the on/off function is best accomplished with a mechanical relay or open-collector/open-drain drive circuit. The drive circuit should be able to sink appropriate current when activated and withstand appropriate voltage when deactivated.

Figure 2. Driving the On/Off Control Pin with an Open-Collector Drive Circuit

The on/off control function, however, can be externally inverted so that the converter will be disabled while the input voltage is ramping up and then "released" once the input has stabilized.

Figure 2a. Inverting On/Off Control Pin Signal and Power-Up Sequencing

For a controlled start-up of one or more LSN-D5's, or if several output voltages need to be powered-up in a given sequence, the On/Off Control pin can be pulled high (external pull-up resistor, converter disabled) and then driven low with an external open collector device to enable the converter.

#### **Output Overvoltage Protection**

LSN D5 SIP Series DC/DC converters do not incorporate output overvoltage protection. In the extremely rare situation in which the device's feedback loop is broken, the output voltage may run to excessively high levels (Vout = Vin). If it is absolutely imperative that you protect your load against any and all possible overvoltage situations, voltage limiting circuitry must be provided external to the power converter.

#### **Output Overcurrent Detection**

Overloading the output of a power converter for an extended period of time will invariably cause internal component temperatures to exceed their maximum ratings and eventually lead to component failure. High-current-carrying components such as inductors, FET's and diodes are at the highest risk. LSN D5 SIP Series DC/DC converters incorporate an output overcurrent detection and shutdown function that serves to protect both the power converter and its load.

If the output current exceeds it maximum rating by typically 70% (17 Amps) or if the output voltage drops to less than 98% of it original value, the LSN D5's internal overcurrent-detection circuitry immediately turns off the converter, which then goes into a "hiccup" mode. While hiccupping, the converter will continuously attempt to restart itself, go into overcurrent, and then shut down. Under these conditions, the average output current will be approximately 400mA, and the average input current will be approximately 70mA. Once the output short is removed, the converter will automatically restart itself.

#### **Output Voltage Trimming**

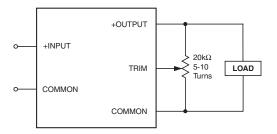

Allowable trim ranges for each model in the LSN D5 SIP Series are ±10%. Trimming is accomplished with either a trimpot or a single fixed resistor. The trimpot should be connected between +Output and Common with its wiper connected to the Trim pin as shown in Figure 3 below.

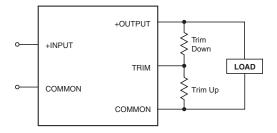

A trimpot can be used to determine the value of a single fixed resistor which can then be connected, as shown in Figure 4, between the Trim pin and +Output to trim down the output voltage, or between the Trim pin and Common to trim up the output voltage. Fixed resistors should have absolute TCR's less than 100ppm/°C to ensure stability.

The equations below can be used as starting points for selecting specific trimresistor values. Recall, untrimmed devices are guaranteed to be  $\pm 1\%$  accurate.

Adjustment beyond the specified ±10% adjustment range is not recommended.

Figure 3. Trim Connections Using a Trimpot

Note: Install either a fixed trim-up resistor or a fixed trim-down resistor depending upon desired output voltage.

Figure 4. Trim Connections Using Fixed Resistors

| Model                          | Trim Equations                                                             |

|--------------------------------|----------------------------------------------------------------------------|

| LCN 1/10 DE                    | $R_{T_{DOWN}}(k\Omega) = \frac{1.62(V_O - 0.8)}{1 - V_O} - 1$              |

| LSN-1/10-D5                    | $R_{T_{UP}}(k\Omega) = \frac{1.296}{V_0 - 1} - 1$                          |

| LSN-1.2/10-D5                  | $R_{T_{DOWN}}(k\Omega) = \frac{2.49(V_0 - 0.8)}{1.2 - V_0} - 2.37$         |

| L3N-1.2/10-D3                  | $R_{T_{UP}}(k\Omega) = \frac{1.992}{V_0 - 1.2} - 2.37$                     |

| LSN-1.5/10-D5<br>LSN-1.8/10-D5 | $R_{T_{DOWN}}(k\Omega) = \frac{2.37(V_O - 0.8)}{V_{O_{NOM}} - V_O} - 4.99$ |

| LSN-2/10-D5<br>LSN-2.5/10-D5   | $R_{T_{UP}}(k\Omega) = \frac{1.896}{V_0 - V_0} - 4.99$                     |

| LSN-3.3/10-D5                  | $R_{T_{DOWN}}(k\Omega) = \frac{7.5(V_0 - 0.8)}{V_{O_{NOM}} - V_0} - 4.99$  |

| L3N-3.3/10-23                  | $R_{T_{UP}}(k\Omega) = \frac{6}{V_O - V_{ONOM}} - 4.99$                    |

| LSN-3.8/10-D5                  | $R_{T_{DOWN}}(k\Omega) = \frac{7.5(V_O - 0.8)}{3.8 - V_O} - 13$            |

| 2311-3.0/10-23                 | $R_{T_{UP}}(k\Omega) = \frac{6}{V_O - 3.8} - 13$                           |

Note: Resistor values are in  $k\Omega$ . Accuracy of adjustment is subject to tolerances of resistors and factory-adjusted, initial output accuracy. Vo = desired output voltage.  $Vo_{NOM} = nominal$  output voltage.

#### **Output Reverse Conduction**

Many DC/DC converters using synchronous rectification suffer from Output Reverse Conduction. If those devices have a voltage applied across their output before a voltage is applied to their input (this typically occurs when another power supply starts before them in a power-sequenced application),

they will either fail to start or self destruct. In both cases, the cause is the "freewheeling" or "catch" FET biasing itself on and effectively becoming a short circuit.

LSN D5 SIP DC/DC converters are not damaged from Output Reverse Conduction. They employ proprietary gate drive circuitry which makes them immune to applied voltages during the startup sequence. If you are using an external power source paralleled with the LSN, be aware that during the start up phase, some low impedance condition or transient current may be absorbed briefly into the LSN output terminals before voltage regulation is fully established. You should insure that paralleled external power sources are not disrupted by this condition during LSN start up.

#### **Thermal Considerations and Thermal Protection**

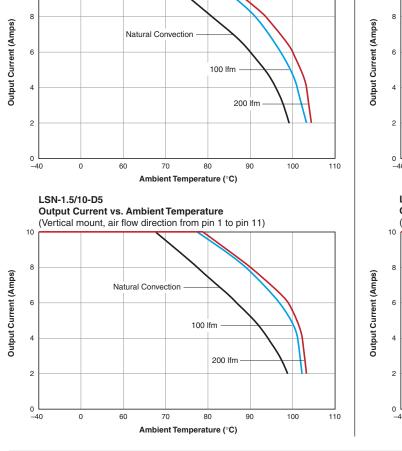

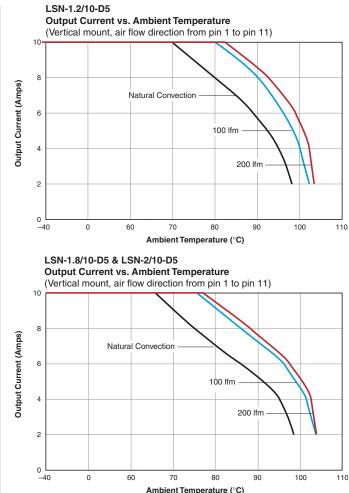

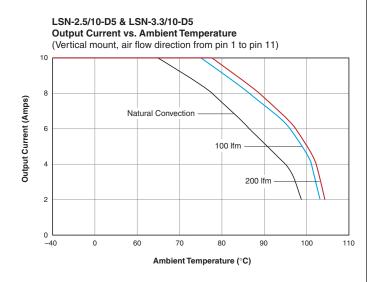

**Output Current vs. Ambient Temperature**

(Vertical mount, air flow direction from pin 1 to pin 11)

LSN-1/10-D5

The typical output-current thermal-derating curves shown below enable designers to determine how much current they can reliably derive from each model of the LSN D5 SIP's under known ambient-temperature and air-flow conditions. Similarly, the curves indicate how much air flow is required to reliably deliver a required output current at known temperatures.

The highest temperatures in LSN D5 SIP's occur at their output inductor, whose heat is generated primarily by I<sup>2</sup>R losses. The above curves were developed using thermocouples to monitor the inductor temperature and varying the load to keep that temperature below +110°C under the assorted conditions of air flow and air temperature. Once the temperature exceeds

+115°C (approx.), the thermal protection will disable the converter. Automatic restart occurs after the temperature has dropped below +110°C.

In all cases below, the DUT's were vertical-mount models, and the direction of air flow was parallel to the unit in the direction from pin 1 to pin 11.

As you may deduce from the above curves and can observe in the efficiency curves on the next page, LSN D5 SIP's are more efficient at lower current levels. Also, I²R losses in the output inductor are significantly less at lower currents. Consequently, LSN D5 SIP's deliver very impressive temperature performance if operating at less than full load.

Lastly, when LSN D5 SIP's are installed in system boards, they are obviously subject to numerous factors and tolerances not taken into account above. If you are attempting to extract the most current out of these units under demanding temperature conditions, we advise you to monitor the output-inductor temperature to ensure it remains below +110°C at all times.

#### Thermal Performance for "H" Models

Enhanced thermal performance can be achieved when LSN D5 SIP's are mounted horizontally ("H" models) and the output inductor (with its electrically isolating, thermally conductive pad installed) is thermally coupled to a copper plane/pad (at least 0.55 square inches in area) on the system board. Your conditions may vary, however our tests indicate this configuration delivers a 16°C to 22°C improvement in ambient operating temperatures.

# Typical Performance Curves for LSN D5 SIP Series

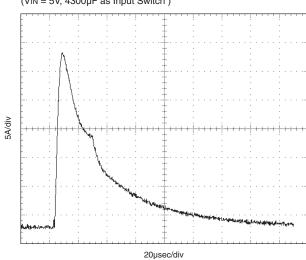

# Input Inrush Current

$(VIN = 5V, 4300\mu F as Input Switch)$

#### Input Reflected Ripple Current

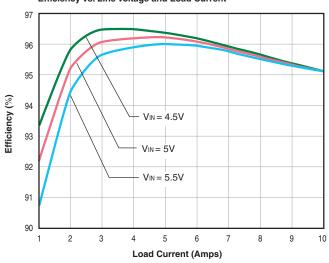

#### LSN-3.3/10-D5 Efficiency vs. Line Voltage and Load Current

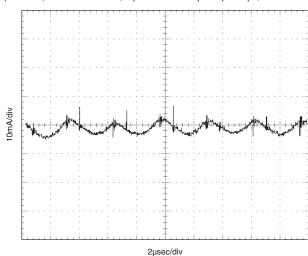

#### Input Reflected Ripple Current

(VIN = 5V, VOUT = 3.3V/10A, Input Filter =  $220\mu F/12\mu H/33\mu F$ , COUT = NA

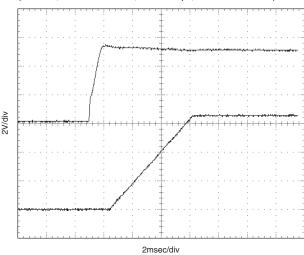

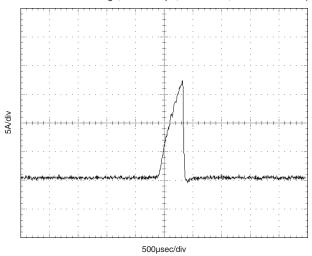

#### Power-Up From VIN

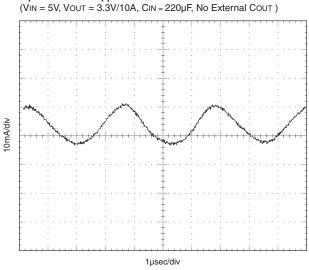

$(VIN = 5V, VOUT = 3.3V/10A, CIN = 220\mu F, No External COUT)$

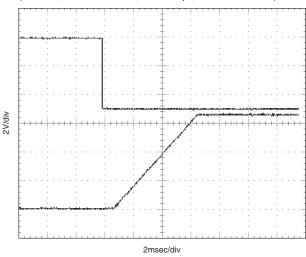

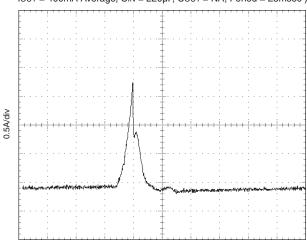

#### Power-Up From Enable

(VIN = 5V, VOUT = 3.3V/10A, CIN =  $220\mu F$ , No External COUT)

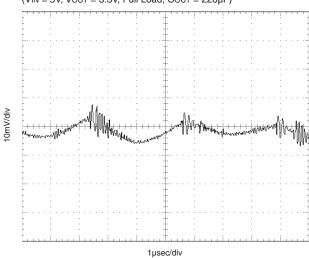

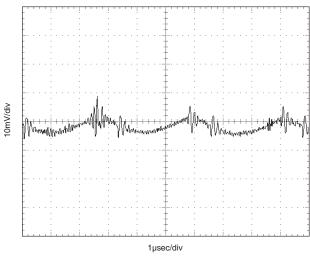

#### Output Ripple/Noise

(VIN = 5V, VOUT = 3.3V, Full Load, COUT =  $220\mu F$ )

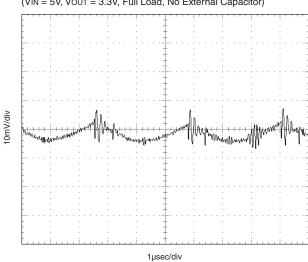

#### **Output Ripple/Noise**

(VIN = 5V, VOUT = 3.3V, Full Load, No External Capacitor)

#### **Output Ripple/Noise**

(VIN = 5V, VOUT = 3.3V, No Load, No External Capacitor)

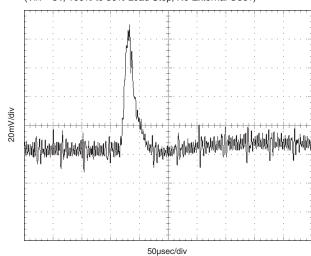

#### **Dynamic Load Response**

(VIN = 5V, 100% to 50% Load Step, No External Cout)

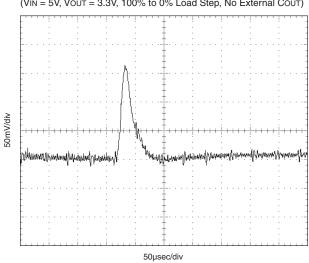

#### **Dynamic Load Response**

(VIN = 5V, VOUT = 3.3V, 100% to 0% Load Step, No External COUT)

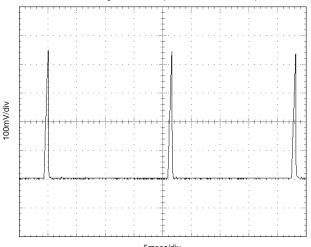

# **Output Hiccup**

(VIN = 5V, VOUT = Short, IIN = 70mA Average, IOUT = 400mA Average, CIN = 220µF, No External COUT)

# **Short-Circuit Output Current**

(VIN = 5V, VOUT = Short, IIN = 70mA Average, IOUT = 400mA Average, CIN = 220µF, COUT = NA, Period = 25msec)

# Input Current with Short Circuit at Output

(VIN = 5V, VOUT = Short, IIN = 70mA Average, IOUT = 400mA Average, CIN =  $220\mu F$ , COUT = NA, Period = 25msec)

2.5msec/div

#### EMI CONDUCTED/RADIATED EMISSIONS

If you're designing with EMC in mind, please note that all of C&D's LSN D5 DC/DC Converters have been characterized for conducted and radiated emissions in our EMI/EMC laboratory. Testing is conducted in an EMCO 5305 GTEM test cell utilizing EMCO automated EMC test software. Conducted/Radiated emissions are tested to the limits of FCC Part 15, Class B and CISPR 22 (EN 55022), Class B. Correlation to other specifications can be supplied upon request. For corresponding emissions plots to FCC and CISPR 22 for model LSN-5/10-D12 (the highest possible output power model) and for LSN-2/10-D3 (representing the highest input current models) see LSN-10A D12 and LSN-10A D3 data sheets for reference. These respective curves are representative of all LSN models. Contact C&D's Applications Engineering Department for more details.

# RoHS compliance ("-C" suffix)

Selected models use materials which are compatible with the Reduction of Hazardous Substances (RoHS) directive. Contact C&D Technologies (DATEL).

#### **Functional Options**

#### Remote Sense Pin Removed ("B" suffix)

These devices have their +Sense pin (pin 3) removed, and the feedback loop is closed through the +Vou $\tau$  path. The 10.5 $\Omega$  resistor in Figure 1 is installed in both standard and "B" models. See the Output Sense Function.

#### Horizontal Mounting ("H" suffix)

This packaging configuration reduces above-board height to 0.35" (8.89mm) including the "pad." For "H" models, a thermally conductive, electrically insulating "pad" is factory installed on the output inductor. The pad material is Bergquist Sil Pad 400. The pad size is 0.4 x 0.5 x 0.009 inches (10.16 x 12.7 x 0.23mm). This configuration can significantly improve thermal performance. See Thermal Derating for details.

#### Reversed pin vertical mounting ("J" suffix)

This additional mechanical configuration consists of a low-profile pin header attached to the reverse side of the converter. It allows the LSN series to be mechanically compatible with Tyco's "keep out area."

#### Other Options and Modifications

Other options include a positive polarity (pull low to disable) on the On/Off Control. Contact C&D directly to discuss these and other possible modifications.

#### Examples

LSN-1.8/10-D5 Vertical-mount. Sense function on pin 3. No pin 9. LSN-1.8/10-D5B Vertical-mount. Pin 3 (+Sense) removed. No pin 9. LSN-1.8/10-D5H Horizontal-mount. Sense function on pin 3. No pin 9. LSN-1.8/10-D5BH Horizontal-mount. Pin 3 (+Sense) removed. No pin 9. LSN-1.8/10-D5J Reverse pin vertical-mount. Sense function on pin 3.

No pin 9.

# TECHNOLOGIES

C&D Technologies, Inc.

11 Cabot Boulevard, Mansfield, MA 02048-1151 U.S.A. Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356

www.cd4power.com **ISO 9001 REGISTERED**  email: sales@cdtechno.com

DS-0516A

© 2007 C&D Technologies, Inc.

C&O Technologies, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

USA: Tucson (Az), Tel: (800) 547 2537, email: sales@cdtechno.com Canada: Toronto, Tel: (866) 740 1232, email: toronto@cdtechno.com UK: Milton Keynes, Tel: +44 (0)1908 615232, email: mk@cdtechno.com

France: Montigny Le Bretonneux, Tel: +33 (0)1 34 60 01 01, email: france@cdtechno.com

Germany: München, Tel: +49 (0)89-544334-0, email: ped.munich@cdtechno.com Japan: Tokyo, Tel: 3-3779-1031, email: sales\_tokyo@cdtechno.com

Osaka, Tel: 6-6354-2025, email: sales osaka@cdtechno.com Website: www.cd4power.jp

China: Shanghai, Tel: +86 215 027 3678, email: shanghai@cdtechno.com

Guangzhou, Tel: +86 208 221 8066, email: guangzhou@cdtechno.com