### **Advanced Products**

### **FUJITSU**

October 1986 Edition 1.0

### MBL8049N/E/H MBL8039N/E/H

NMOS Single-Chip 8-Bit Microcomputer

#### Description

The Fujitsu MBL8049/MBL8039 is a totally self-contained 8-bit parallel one-chip microcomputer fabricated with an N-channel silicon gate MOS process.

The MBL8049 has a 2K × 8 ROM program memory, a 128 × 8 RAM data memory, 27 I/O ports, an 8-bit timer/counter and clock generator on chip. A single power supply of +5V is used. The MBL8039 is identical to the MBL8049 except without program memory. It can be used with external memory for system prototyping and preproduction systems.

The design is optimized for low cost, high performance applications because the MBL8049/MBL8039 is fabricated on a single silicon chip and can be used for applications that require additional expansion of ROMs, RAMs, I/O port, etc.

This microcomputer permits external program operation and a single-step operation mode. Low power applications are possible by using the stand-by mode feature.

The MBL8049/MBL8039 is packaged in a standard 40-pin DIP package and operation is guaranteed from 0°C to 70°C.

#### **Features**

- 8-bit Parallel Microcomputer

- 12-bit Addressing

- 96 Instructions: 70% Single

- 1.875µs Cycle (E-Version) 2.5µs Cycle (N-Version) All Instructions are 1 or 2 Cycles.

- 2K x 8 ROM (MBL8049 only)

128 x 8 RAM

27 I/O Lines

- Interval Timer/Event Counter

- Single Level Interrupt Capability

- Resident Clock Generator (External Frequency Source)

- External Input Capability

- Easily Expandable Memory

- and I/O ■ 8 Level Stack

- External Program Mode Capability

- Low Power Stand-by Mode

- Capability

Single +5V Power Supply

- N-channel Silicon Gate E/D MOS Process

- Standard 40-Pin DIP

MBL8049: Compatible with

- MBL8049: Compatible with Intel 8049

MBL8039: Compatible with Intel 8039

Portions reprinted by permission of Intel Corporation, Copyright © 1985 Intel Corporation. Compilation and additional materials Copyright © 1985 by Fujitsu Limited, Tokyo, Japan, and Fujitsu Microelectronics, Inc., Santa Clara, California, U.S.A. Fujitsu Limited is a licensee of Intel Corporation and authorized to produce alternate source products.

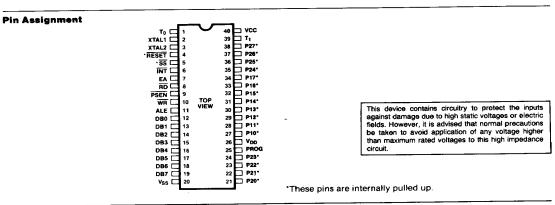

**Pin Description**

| Pin No.                  | Pin Name            | Symbol             | Function                                                                                                                                                                                                                                                                                                |

|--------------------------|---------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | Sense               | То                 | This pin has the following functions according to instructions.  1) Output of clock (\( \phi \) 1) 2MHz at 6 MHz XTAL  2) Condition input for a Conditional Branch                                                                                                                                      |

|                          |                     |                    | This is an input terminal for the internal Clock Generator to be connected to a terminal of the external crystal.                                                                                                                                                                                       |

| 2                        | Crystal 1           | XTAL 1             | Also, this pin can be used as the input from an external clock source.                                                                                                                                                                                                                                  |

|                          |                     |                    | Note: This input is not compatible with TTL levels.                                                                                                                                                                                                                                                     |

| 3                        | Crystal 2           | XTAL 2             | This is an input terminal for the internal Clock Generator be connected to the external crystal.                                                                                                                                                                                                        |

|                          |                     |                    | Note: This input is not compatible with TTL level.                                                                                                                                                                                                                                                      |

| 4                        | Reset               | RESET              | This input forces the MPU to be reset or initialized.                                                                                                                                                                                                                                                   |

| ·                        | rieser              | MEGET              | Note: This input is not compatible with TTL level.                                                                                                                                                                                                                                                      |

| 5                        | Single Step         | SS                 | This input is used in conjunction with ALE for single step operation.                                                                                                                                                                                                                                   |

| 6                        | Interrupt           | INT                | This input is used to request an external interrupt.                                                                                                                                                                                                                                                    |

| 7                        | External<br>Address | EA                 | When EA goes high while RESET is low, an external address (memory) can be used as the external program operation mode.                                                                                                                                                                                  |

| 8                        | Read                | RD                 | This output is used as a strobe signal for an input of data from the data bus port (DB port). Also, it can be used as a read-enable signal when using an external data memory.                                                                                                                          |

| 9                        | Program<br>Store    | PSEN               | This output signal is generated at a fetch cycle in the external program operation mode.                                                                                                                                                                                                                |

|                          | Enable              |                    | It is used as an enable signal for an external program memory.                                                                                                                                                                                                                                          |

| 10                       | Write               | WR                 | This output is a strobe signal for a data output from the DB port.                                                                                                                                                                                                                                      |

|                          |                     |                    | Also, it can be used as a write-enable signal for an external data memory.                                                                                                                                                                                                                              |

|                          | Address             |                    | This output signal is generated at the beginning of a fetch cycle both in the internal and external program memory operations.                                                                                                                                                                          |

| 11                       | Latch<br>Enable     | ALE                | This output is used as a synchronizing signal with an external circuit and also, as a strobe signal for address outputs $(A_0$ thru $A_7)$ of the DB port in the external program operation mode.                                                                                                       |

| 12                       | Data Bus            | DB0                | These pins are used as a bidirectional 8-bit input/output port (DB port).                                                                                                                                                                                                                               |

| thru<br>19               | Port                | thru<br>DB7        | When an external memory is used as a program memory or data memory, this port is used as an address bus $(A_0 \text{ thru } A_7)$ or data input/output port, respectively.                                                                                                                              |

| 20                       | Power<br>Supply     | V <sub>SS</sub>    | This pin is used as the Ground (GND) terminal.                                                                                                                                                                                                                                                          |

| 21<br>thru<br>2 <b>4</b> | Port 2              | P20<br>thru<br>P23 | These are the lower four bits of a quasi-bidirectional input/output port (P2 port) which are used as address outputs (A <sub>8</sub> thru A <sub>11</sub> ) in a fetch cycle of the external program memory operation mode. When an expansion I/O instruction is executed, these are switched to an I/O |

### Pin Description (Continued)

| Pin No.          | Pin Name        | Symbol                                     | Function                                                                                                                                              |

|------------------|-----------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25               | Program         | PROG                                       | This output is used as a strobe signal for an I/O expander (MBL8243) when performing an expansion I/O instruction.                                    |

| 26               | Power<br>Supply | V <sub>DD</sub>                            | This is used as the power supply terminal (+5V) for the built-in RAM.                                                                                 |

| 27<br>thru<br>34 | Port 1          | P1 <sub>0</sub><br>thru<br>P1 <sub>7</sub> | This is a quasi-bidirectional input/output port (P1 port)                                                                                             |

| 35<br>thru<br>38 | Port 2          | P2 <sub>4</sub><br>thru<br>P2 <sub>7</sub> | These are the upper four bits of the quasi-bidirectional input/output port 2 (P2).                                                                    |

| 39               | Sense           | Т <sub>1</sub>                             | This pin has the following functions according to the instruction given:  1) Event Input for Event Counter  2) Condition Input for Conditional Branch |

| 40               | Power<br>Supply | V <sub>CC</sub>                            | This is used as the power supply terminal (+5V). In stand-by operation mode this terminal is connected to GND.                                        |

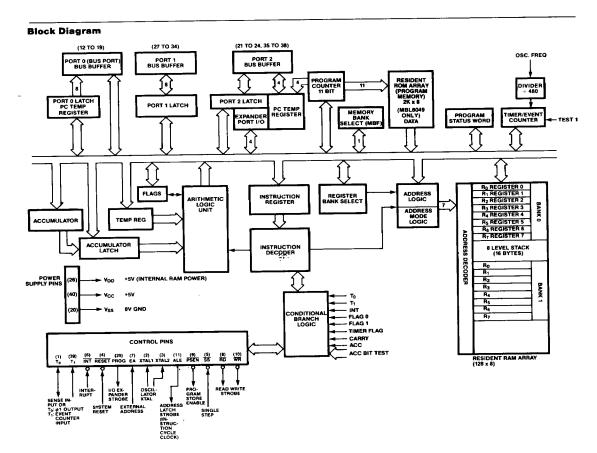

### Functional Descriptions for Basic Blocks

| Block Name                 | Function                                                                                                                                                                                                                                     |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | A master clock signal within a frequency range of 1MHz to 6MHz is supplied from the built-in Clock Generator using a external crystal and capacitor network, or from an external signal source.                                              |

| Clock Generation Circuitry | The frequency of the master clock is divided through the 1/3 Frequency Divider to generate a state clock signal. Then, the frequency of the state clock is divided through the 1/5 Frequency Divider to generate a final cycle clock signal. |

|                            | The state clock can be transferred to the $T_0$ terminal by an instruction.                                                                                                                                                                  |

|                            | The cycle clock is used for internal operations and is also available on the ALE terminal.                                                                                                                                                   |

|                            | Three bidirectional or quasi-bidirectional 8-bit I/O ports and three input terminals are provided for signal inputs and outputs.                                                                                                             |

| I/O Part                   | Port 0 (Bus Port) and the lower 4 bits of Port 2 shown in the Block Diagram are used for access to external memories or I/O expanders.                                                                                                       |

|                            | In the MBL8049, programs are stored in the built-in ROM (2K Bytes). Also, the contents in the ROM can be used as data fo some instructions.                                                                                                  |

|                            | The built-in RAM (128 bytes) is used for general register area, stack area and working area.                                                                                                                                                 |

| Built-in ROM and RAM       | ROM is expandable up to a total of 4K Bytes with externally attached ROM by switching the memory bank.                                                                                                                                       |

|                            | RAM is expandable by an additional 256 Bytes with externally attached RAM.                                                                                                                                                                   |

|                            | MBL8039 does not have any built-in ROM. It uses external ROM for program storing.                                                                                                                                                            |

| Program Counter            | The program counter is an 11-bit register which indicates a<br>fetch address of program memory and is incremented by<br>every execution of an instruction.                                                                                   |

#### Functional Descriptions for Basic Blocks (Continued)

| Block Name                                 | Function                                                                                                                                                                                                                                      |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Register                       | The Instruction Register is an 8-bit register which stores a fetched instruction in a fetch cycle.                                                                                                                                            |

| Instruction Decoder                        | The Instruction Decoder decodes the instruction stored in the Instruction register and generates various control signals for both internal circuitry and external peripherals.                                                                |

| Arithmetic Logic Unit (ALU)                | Various operations such as addition, subtraction, comparison, etc., are executed in the ALU. Operation to be executed is determined from the decoding of an instruction.                                                                      |

|                                            | The Interval Timer/Event Counter is an 8-bit register which can be controlled by instruction execution. The interval timer mode or event counter mode can be designated by instruction execution, as well.                                    |

|                                            | This register is not initialized by the RESET signal. In the interval timer mode, the register can count up the frequency signal which is generated by dividing the cycle clock frequency by 32.                                              |

|                                            | When the source oscillation frequency is 6MHz, this enables the register to count a time interval of up to $20.48$ ms with resolution of $80\mu$ s.                                                                                           |

| Interval Timer/Event Counter               | In this mode, the register generates an interrupt vector address (Address 07), if the register overflows from (FF) $_{16}$ to (00) $_{16}$ .                                                                                                  |

|                                            | Even if an overflow occurs, the register can continue to count up. This enables the register to count a longer time interval by using proper software. In the event counter mode, the register counts on the falling edge of the $T_1$ input. |

|                                            | In this mode, the features of the register other than the counting trigger are the same as those in the interval timer mode.                                                                                                                  |

|                                            | Note: The $T_1$ input pulse has a 500ns Min. pulse width and a 7.5 $\mu s$ Min. cycle time at 6MHz of source oscillation.                                                                                                                     |

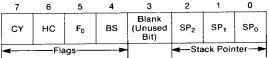

|                                            | The Status Register is an 8-bit register which consists of four bits for flags, three bits for the Stack Pointer and an unused bit.                                                                                                           |

| Status Register Including<br>Stack Pointer | The flag bits indicate the status of the MPU.                                                                                                                                                                                                 |

| Stack i Office                             | The Stack Pointer indicates with its three bits, an address in the stack area to be used in the next subroutine call or interrupt.                                                                                                            |

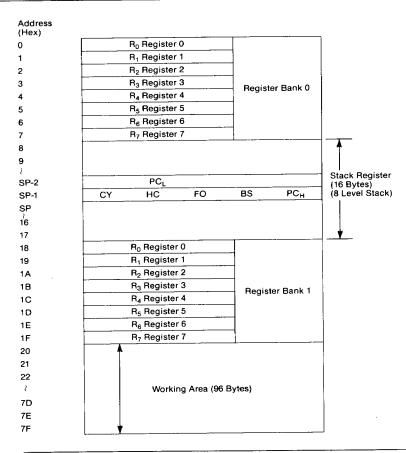

#### Resident Data Memory Map (RAM)

#### Status Register (PSW)

The Status Register is an 8-bit register configured as shown in the following figure. The upper four bits are used for flags to indicate the status of the MPU, and when a sub-routine call or an interrupt occurs, the contents of the program counter is transferred to one of the 8 register pairs of the Stack Register as determined by the lower three bits of the Status Register. The remaining one bit is an unused bit.

#### Flags

CY (Carry): When an overflow occurs in the Accumulator during an operation in the ALU, "1" is set in this bit.

HC (Half Carry): When an overflow occurs from Bit 3 to Bit 4 in the accumulator as a result of an addition, "1" is set in this bit.

F<sub>0</sub>(User Flag): This flag can be controlled as a user flag by the proper instruction.

BS (Bank select): This flag can be controlled to select a Register Bank by an instruction. When BS = 0, the Register Bank 0 is selected. When BS = 1, the Register Bank 1 is selected.

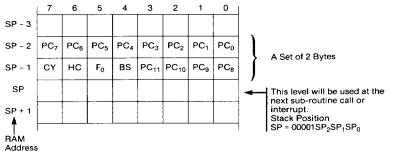

#### Stack Register (8 Level Capability)

The Stack Register occupies 16-bytes of memory within the on-board RAM. It is configured into eight levels of two bytes each as shown in Figure 1.

Stack Pointer (SP) In Figure 1., "SP" indicates the stack level to be used for the next sub-routine call or interrupt. The Stack Pointer generates one of eight address codes and resides in the lower three bits of the status register.

SP = 0 0 0 0 1 SP<sub>2</sub>SP<sub>1</sub>SP<sub>0</sub>

#### Program Counter (PC)

In Figure 1., "PC<sub>n</sub>" indicates the individual bit contents of each of the Program Counter bits

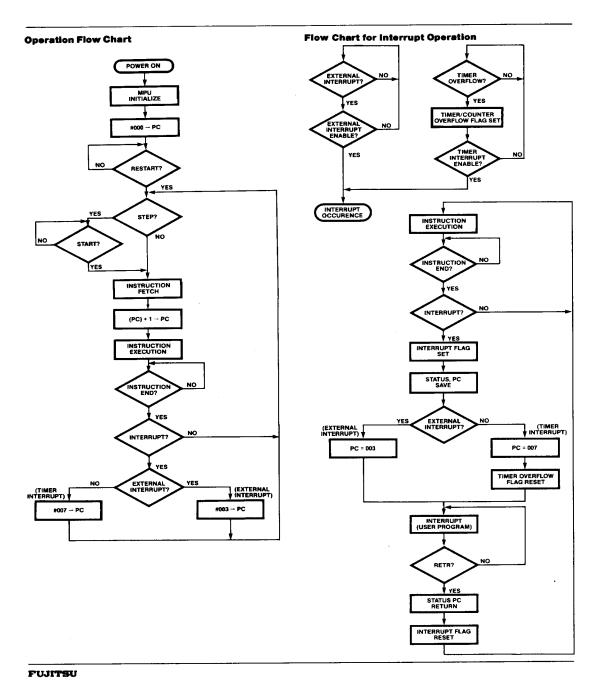

#### Interrupt Operation

There are two interrupt modes, external interrupts, and timer/counter interrupts.

When either interrupt occurs, an interrupt flag is set and upon completion of the executing instruction the interrupt is processed.

Interrupt processing is as follows:

- 1. The contents of the Status Register and Program Counter are saved on the Stack.

- 2. Program flow jumps to the address specified at address three (3) for external interrupts and address seven (7) for timer/counter interrupts.

- 3. Completion of the interrupt processing occurs upon execution of the RETR (Return and Restore Status) instruction.

- 4. The contents of the program counter and status register are restored from the stack, the interrupt flag is reset to be ready for the next interrupt, and program execution continues from where it left off.

Timer/counter interrupts occur when the overflow flag is set as a result of an overflow from the Timer/Counter.

External interrupts occur when a low level input is applied to the "INT" input.

External interrupts have priority over Timer/Counter interrupts, so if both interrupts occur at the same time the external interrupt will be processed first. After completion of the external interrupt and resetting of the interrupt flag the Timer/ Counter interrupt will be processed.

#### Instructions

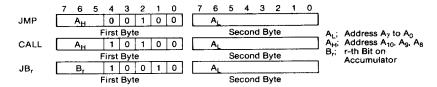

All instructions are either one or two bytes long and execute in one or two cycles. Addressing modes are classified into direct, expanded, indirect, immediate and implied.

Instruction Mode

f

1) 1 Byte Instruction

Implied Addressing Mode

r f Register Indirect Addressing Mode

r Register Direct Addressing Mode

2) 2 Byte Instruction

ΩP Immediate Addressing Mode

f AL Expanded Addressing Mode

f: Instruction Operation Set r: Register Set OP: Operand Data A<sub>H</sub>, A<sub>L</sub>: Operand Address

Figure 1.

2-29

#### **Instruction Set Summary**

#### Accumulator

|                               |                        | OP   |      |       | Fla | 9  |    |    |                                       |

|-------------------------------|------------------------|------|------|-------|-----|----|----|----|---------------------------------------|

| Operation                     | Mnemonic               | Code | Byte | Cycle | CY  | нс | Fo | F, | Note                                  |

| Add register to A             | ADD A.R.               | 6X   | 1    | 1     | ٠   | 3  | _  | _  | $(R_r) + (A) \rightarrow (A)$         |

| Add data memory to A          | ADD A,@R <sub>0</sub>  | 60   | 1    | 1     | •   | •  | _  | _  | $((R_0)) + (A) \rightarrow (A)$       |

|                               | ADD A,@R <sub>1</sub>  | 61   | 1    | 1     | •   | •  | _  | _  | $((R_1)) + (A) - (A)$                 |

| Add immediate to A            | ADD A,#data            | 03   | 2    | 2     | •   | •  |    | _  | data + (A) → (A)                      |

| Add register with carry       | ADDC A,R,              | 7X   | 1    | 1     | •   | •  | _  | _  | $(R_r) + (A) + (C) \rightarrow (A)$   |

| Add data memory with carry    | ADDC A,@R <sub>0</sub> | 70   | 1    | 1     | •   | •  | _  | _  | $((R_0)) + (A) + (C) - (A)$           |

|                               | ADDC A,@R <sub>1</sub> | 71   | 1    | 1     | •   | •  | _  | _  | $((R_1)) + (A) + (C) - (A)$           |

| Add immediate to A with carry | ADDC A,#data           | 13   | 2    | 2     | •   | •  | _  | _  | data + (A) + (C) → (A)                |

| And register to A             | ANL A,R,               | 5X   | 1    | 1     | _   | _  | _  | _  | $(H_r)\cap(A) \dashv (A)$             |

| And data memory to A          | ANL A,@R <sub>0</sub>  | 50   | 1    | 1     | _   |    | _  | _  | $((R_0)) \cap (A) \rightarrow (A)$    |

| ŕ                             | ANL A.@R1              | 51   | 1    | 1     |     | _  | _  | _  | $((R_1)) \cap (A) \rightarrow (A)$    |

| And immediate to A            | ANL A,#data            | 53   | 2    | 2     | _   | _  | -  | _  | data $\cap$ (A) $\rightarrow$ (A)     |

| Clear A                       | CLR A                  | 27   | 1    | 1     | _   | _  | _  | _  | 0 → (A)                               |

| Complement A                  | CPL A                  | 37   | 1    | 1     | _   | _  | _  | -  | $(\bar{A}) \to (A)$                   |

| Decimal Adjust A              | DA A                   | 57   | 1    | 1     | ٠   | _  | _  |    | Note (1)                              |

| Decrement A                   | DEC A                  | 07   | 1    | 1     | -   | _  | _  | _  | (A) -1 → (A)                          |

| Increment A                   | INC A                  | 17   | 1    | 1     | _   | _  | _  | -  | (A) + 1 (A)                           |

| Or register to A              | ORL A.R.               | 4X   | 1    | 1     | _   | _  | _  | _  | $(R_r) \cup (A) \rightarrow (A)$      |

| Or data memory to A           | ORL A,@Ro              | 40   | 1    | 1     | _   | _  | _  | -  | $((R_0)) \cup (A) \rightarrow (A)$    |

| •                             | ORL A,@R,              | 41   | 1    | 1     | _   | _  | _  | _  | $((R_1) \cup (A) \rightarrow (A)$     |

| Or immediate to A             | ORL A,#data            | 43   | 2    | 2     | -   | -  | _  | -  | data ∪ (A) → (A)                      |

| Rotate A left                 | RL A                   | E7   | 1    | 1     | _   | _  | _  | _  | ثتتتت                                 |

| Rotate A left with carry      | RLC A                  | F7   | 1    | 1     | •   | _  | _  | _  | 40-41111                              |

| Rotate A right                | RR A                   | 77   | 1    | 1     |     | _  | _  | _  | رْتىتىتىن                             |

| Rotate A right with carry     | RRC A                  | 67   | 1    | 1     | •   | _  | _  | _  | ريسسسي                                |

| SWAP nibbles of A             | SWAP A                 | 47   | 1    | 1     | _   | _  | _  |    | $(A_{4-7}) = (A_{0-3})$               |

| Exclusive Or register to A    | XRL A,R,               | DX   | 1    | 1     | _   | _  | _  | _  | $(R_r) \bigoplus (A) \rightarrow (A)$ |

| Exclusive Or data memory to A | XRL A,@R <sub>0</sub>  | D0   | 1    | 1     | _   | _  | _  | _  | ((R <sub>0</sub> ))⊕(A) - (A)         |

| IO A                          | XRL A.@R <sub>1</sub>  | D1   | 1    | 1     | _   |    | _  | _  | $\{(R_1)\}\bigoplus(A)\rightarrow(A)$ |

| Exclusive Or immediate to A   | XRL A,#data            | D3   | 2    | 2     | _   |    |    |    | data⊕(A) → (A)                        |

## Instruction Set Summary (Continued)

#### Input/Output

|                           |                        | OP   |      |       | Fla | 9  |    |                |                                                               |

|---------------------------|------------------------|------|------|-------|-----|----|----|----------------|---------------------------------------------------------------|

| Operation                 | Mnemonic               | Code | Byte | Cycle | CY  | HC | Fo | F <sub>1</sub> | Note                                                          |

| And immediate to BUS      | ANL BUS,#data          | 98   | 2    | 2     | _   | _  | _  | _              | data ∩ (BUS) → (BUS)                                          |

| Ρ,                        | ANL P1,#data           | 99   | 2    | 2     | _   | _  | _  | _              | data $\cap$ (P <sub>1</sub> ) $\rightarrow$ (P <sub>1</sub> ) |

| P <sub>2</sub>            | ANL Po#data            | 9A   | 2    | 2     | _   | _  | _  | _              | data $\cap (P_2) \rightarrow (P_2)$                           |

| And A to Expander Port    | ANLD P <sub>P</sub> ,A | 9X   | 1    | 2     | -   | -  | _  |                | $(A)\cap(P_P)\to(P_P)$                                        |

| Input BUS to A            | INS A,BUS              | 08   | 1    | 2     | _   | _  | _  | _              | (BUS) → (A)                                                   |

| Port 1 to A               | IN A,P <sub>1</sub>    | 09   | 1    | 2     | _   | _  | _  | _              | $(P_1) \rightarrow (A)$                                       |

| Port 2 to A               | IN A,P <sub>2</sub>    | 0A   | 1    | 2     | _   | _  | _  | _              | $(P_2) \rightarrow (A)$                                       |

| Input Expander port to A  | MOVD A.Pp              | ОХ   | 1    | 2     | -   | _  | _  | _              | $(P_P) \rightarrow (A)_{0-3}$                                 |

|                           |                        |      |      |       |     |    |    |                | 0 → (A) <sub>4-7</sub>                                        |

| Or immediate to BUS       | ORL BUS.#data          | 88   | 2    | 2     | _   | _  | _  | _              | data ∪ (BUS) → (BUS)                                          |

| P <sub>1</sub>            | ORL P1,#data           | 89   | 2    | 2     | _   | -  | _  | _              | data $\cup$ (P <sub>1</sub> ) $\rightarrow$ (P <sub>1</sub> ) |

| P <sub>2</sub>            | ORL Po,#data           | 8A   | 2    | 2     | _   | _  | _  |                | data $\cup$ (P <sub>2</sub> ) $\rightarrow$ (P <sub>2</sub> ) |

| Or A to Expander Port     | ORLD P <sub>P</sub> ,A | 8X   | 1    | 2     | _   | -  | _  | _              | data $\cup$ ( $P_P$ ) $\rightarrow$ ( $P_P$ )                 |

| Output A to BUS           | OUTL BUS,A             | 02   | 1    | 2     | -   | _  | _  | -              | (A) → (BUS)                                                   |

| P <sub>1</sub>            | OUTL P <sub>1</sub> ,A | 39   | 1    | 2     | _   | _  |    | _              | $(A) \rightarrow (P_1)$                                       |

| P <sub>2</sub>            | OUTL P2,A              | 3A   | 1    | 2     | _   | _  | _  | _              | $(A) \rightarrow (P_2)$                                       |

| Output A to Expander Port | MOVD P <sub>P1</sub> A | 3X   | 1    | 2     | _   |    |    | _              | $(A) \rightarrow (P_P)$                                       |

#### **Data Moves**

|                                |                           | OP   |      |       | Fla | g  |                |    |                                       |

|--------------------------------|---------------------------|------|------|-------|-----|----|----------------|----|---------------------------------------|

| Operation                      | Mnemonic                  | Code | Byte | Cycle | CY  | HC | F <sub>0</sub> | F, | Note                                  |

| Move register to A             | MOV A,R,                  | FX   | 1    | 1     | _   |    | _              | _  | $(R_r) \rightarrow (A)$               |

| Move data memory to A          | MOV A,@R <sub>0</sub>     | F0   | 1    | 1     | _   | _  | -              | _  | $((R_0)) \rightarrow (A)$             |

| ·                              | MOV A.@R <sub>1</sub>     | F1   | 1    | 1     | _   | _  | _              | _  | $((R_1)) \rightarrow (A)$             |

| Move immediate to A            | MOV A,#data               | 23   | 2    | 2     | _   | _  | _              | _  | data → (A)                            |

| Move A to register             | MOV R, A                  | AX   | 1    | 1     | _   | -  | _              | _  | $(A) \rightarrow (R_r)$               |

| Move A to data memory          | MOV @ R <sub>0</sub> ,A   | A0   | 1    | 1     | _   | _  | _              | -  | $(A) \rightarrow ((R_0))$             |

|                                | MOV @R <sub>1</sub> ,A    | A1   | 1    | 1     | _   | _  | _              | _  | $(A) \rightarrow ((R_1))$             |

| Move immediate to register     | MOV R,,#data              | вх   | 2    | 2     | _   | _  | _              | _  | data → (R <sub>r</sub> )              |

| Move immediate to data memory  | MOV @R <sub>0</sub> ,#dat | a 80 | 2    | 2     | _   | -  | _              | _  | data $\rightarrow ((R_0))$            |

| ,                              | MOV @R <sub>1</sub> ,#dat | aB1  | 2    | 2     | _   | _  | -              | _  | $data \rightarrow ((R_1))$            |

| Move PSW to A                  | MOV A.PSW                 | C7   | 1    | 1     |     | _  | _              | _  | (PSW) → (A)                           |

| Move A to PSW                  | MOV PSW.A                 | D7   | 1    | 1     | ٠   | *  | •              | _  | (A) → (PSW)                           |

| Move external data memory to A | MOVX A,@R <sub>0</sub>    | 80   | 1    | 2     | -   | -  | _              | -  | $((R_0)) \rightarrow (A)$             |

|                                | MOVX A,@R <sub>1</sub>    | 81   | 1    | 2     | _   |    | _              | _  | $((R_1)) \to (A)$                     |

| Move A to eternal data memory  | MOVX @R <sub>0</sub> ,A   | 90   | 1    | 2     | _   | _  | -              | _  | $(A) - ((R_0))$                       |

| ,                              | MOVX @R <sub>1</sub> ,A   | 91   | 1    | 2     | _   |    | _              | _  | $(A) \rightarrow ((R_1))$             |

| Move to A from current page    | MOVP A,@A                 | A3   | 1    | 2     | _   | _  | _              | _  | $((A)) \rightarrow (A)$               |

| Move to A from page 3          | MOVP3 A,@A                | E3   | 1    | 2     | _   | _  | _              |    | ((A)) within page $3 \rightarrow (A)$ |

| Exchange A and register        | XCH A.R.                  | 2X   | 1    | 1     | _   | _  | _              | _  | $(R_r) \rightrightarrows (A)$         |

| Exchange A and data memory     |                           | 20   | 1    | 1     |     | _  | _              | _  | $((R_0)) \equiv (A)$                  |

|                                | XCH A.@R,                 | 21   | 1    | 1     | _   | -  |                | -  | $((R_1)) \supseteq (A)$               |

| Exchange nibble of A           | XCHD A,@R <sub>0</sub>    | 30   | 1    | 1     | _   | _  | _              | _  | $((R0)_{0-3}) \equiv (A_{0-3})$       |

| and data memory                | XCHD A,@R                 | 31   | 1    | 1     | _   |    | _              | _  | $((R1)_{0-3}) \equiv (A_{0-3})$       |

## Instruction Set Summary (Continued)

#### Registers

|                       |                     | OP   |      |       | Fla | 9  |    |                | _                                 |

|-----------------------|---------------------|------|------|-------|-----|----|----|----------------|-----------------------------------|

| Operation             | Mnemonic            | Code | Byte | Cycle | CY  | нс | Fo | F <sub>1</sub> | Note                              |

| Decrement Register    | DEC R <sub>r</sub>  | СХ   | 1    | 1     | _   |    | -  | _              | $(R_r) \sim 1 \rightarrow (R_r)$  |

| Increment register    | INC R,              | 1X   | 1    | 1     | _   |    | _  | _              | $(R_r) + 1 \rightarrow (R_r)$     |

| Increment data memory | INC @R <sub>0</sub> | 10   | 1    | 1     | _   | _  | -  | _              | $((R_0)) + 1 \rightarrow ((R_0))$ |

| •                     | INC @R1             | 11   | 1    | 1     | -   | _  | _  | _              | $((R_1)) + 1 - ((R_1))$           |

#### Timer/Counter

|                                    |           | OP   |      |       | Fla | g  |    |    | _                     |

|------------------------------------|-----------|------|------|-------|-----|----|----|----|-----------------------|

| Operation                          | Mnemonic  | Code | Byte | Cycle | CY  | нс | Fo | F, | Note                  |

| Disable Timer/Counter<br>Interrupt | DIS TONTI | 35   | 1    | 1     | _   | -  | -  | -  |                       |

| Enable Timer/Counter<br>Interrupt  | EN TONTI  | 25   | 1    | 1     | _   | _  | -  | _  |                       |

| Read Timer/Counter                 | MOV A,T   | 42   | 1    | 1     | _   |    | _  | _  | (T) → (A)             |

| Load Timer/Counter                 | MOV T,A   | 62   | 1    | 1     | _   | _  |    |    | $(A) \rightarrow (T)$ |

| Start Timer                        | STRT T    | 55   | 1    | 1     | _   | _  | _  |    |                       |

| Start Counter                      | STRT CNT  | 45   | 1    | 1     |     | -  |    | _  |                       |

| Stop Timer/Counter                 | STOP TONT | 65   | 1    | 1     | -   | _  | _  |    |                       |

#### Control

|                                    |                      | OP Flag |      |       |    |    |    |    |           |

|------------------------------------|----------------------|---------|------|-------|----|----|----|----|-----------|

| Operation                          | Mnemonic             | Code    | Byte | Cycle | CY | HC | Fo | F, | Note      |

| ble external Interrupt             | DISI                 | 15      | 1    | 1     | _  |    | _  | _  |           |

| ble external Interrupt             | EN I                 | 05      | 1    | 1     | _  | _  | _  | _  |           |

| ole Clock output on T <sub>0</sub> | ENT <sub>0</sub> CLK | 75      | 1    | 1     | _  | _  | -  | -  |           |

| peration                           | NOP                  | 00      | 1    | 1     | -  | -  |    | _  |           |

| t register bank 0                  | SEL RB0              | C5      | 1    | 1     | _  | _  | _  | _  | 0 → (BS)  |

| ct register bank 1                 | SEL RB1              | D5      | 1    | 1     |    |    | _  | _  | 1 → (BS)  |

| ct memory bank 0                   | SEL MB0              | E5      | 1    | 1     |    | _  | -  | _  | 0 → (MBF) |

| ct memory bank 1                   | SEL MB1              | F5      | 1    | 1     |    |    | _  | _  | 1 → (MBF) |

#### **Instruction Set Summary** (Continued)

#### **Branch**

|                             |             | OP   |      |       | Fla | 9  |    |    |                                |

|-----------------------------|-------------|------|------|-------|-----|----|----|----|--------------------------------|

| Operation                   | Mnemonic    | Code | Byte | Cycle | CY  | HC | Fo | F, | Note                           |

| Decrement register and test | DJNZ R addr | EX   | 2    | 2     | _   | -  | -  | -  | (R <sub>r</sub> ) ≠ 0 Note {2) |

| Jump unconditional          | JMP addr    | %4   | 2    | 2     | _   | _  | _  | _  | Unconditional Branch           |

| Jump indirect               | JMPP @A     | В3   | 1    | 2     | _   | -  | _  | _  | Unconditional Branch Note (3)  |

| Jump on Carry ≈ 1           | JC addr     | F6   | 2    | 2     | _   | _  | _  | _  | (C) = 1                        |

| Jump on Carry = 0           | JNC addr    | E6   | 2    | 2     |     | _  | -  | _  | (C) = 0                        |

| Jump on A zero              | JZ addr     | C6   | 2    | 2     | _   | _  | _  | _  | (A) = 0                        |

| Jump on A not zero          | JNZ addr    | 96   | 2    | 2     | _   | _  | _  | _  | (A) ≠ 0                        |

| Jump on To = 1              | JTO addr    | 36   | 2    | 2     | _   | _  | _  | _  | $(T_0) = 1$                    |

| Jump on T <sub>0</sub> = 0  | JNT0 addr   | 26   | 2    | 2     | _   | _  | _  | _  | $(T_0) = 0$                    |

| Jump on $T_1 = 1$           | JT1 addr    | 56   | 2    | 2     |     | -  | _  | _  | (T <sub>1</sub> ) = 1          |

| Jump on T <sub>1</sub> = 0  | JNT1 addr   | 46   | 2    | 2     | _   | _  |    | _  | $(T_1) = 0$                    |

| Jump on F <sub>0</sub> = 1  | JF0 addr    | B6   | 2    | 2     | _   | _  | _  | _  | (F <sub>0</sub> = 1            |

| Jump on F <sub>1</sub> = 1  | JF1 addr    | 76   | 2    | 2     | _   | _  | -  | _  | $(F_1) = 1$                    |

| Jump on timer flag          | JTF addr    | 16   | 2    | 2     | -   | -  | _  |    | ( <u>TF)</u> = 1               |

| Jump on INT = 0             | JN1         | 86   | 2    | 2     | _   | _  | _  | _  | ( <del>INT</del> ) = 0         |

| Jump on accumulator bit     | JBr addr    | %2   | 2    | 2     | _   | _  | _  |    | (A <sub>r</sub> ) = 1          |

#### Subroutine

|                           |           | OP   |      |       | Fla | 9  |    |    |          |

|---------------------------|-----------|------|------|-------|-----|----|----|----|----------|

| Operation                 | Mnemonic  | Code | Byte | Cycle | CY  | HC | Fo | F, | Note     |

| Jump to subroutine        | CALL addr | %4   | 2    | 2     | _   | _  | _  | _  | Note (4) |

| Return                    | RET       | 83   | 1    | 2     | _   | _  | -  | _  | Note (5) |

| Return and restore status | RETR      | 90   | 1    | 2     | •   | •  | •  | _  | Note (6) |

#### Flags

|                   |          | OP   |      |       | Fle | 9  |    |    | _                                    |

|-------------------|----------|------|------|-------|-----|----|----|----|--------------------------------------|

| Operation         | Mnemonic | Code | Byte | Cycle | CY  | HC | Fo | F, | Note                                 |

| Clear carry       | CLR C    | 97   | 1    | 1     | z   | _  | _  | _  | 0 → (C)                              |

| Complement carry  | CPL C    | A7   | 1    | 1     | CP  | _  | _  | _  | $(\overline{C}) \rightarrow (C)$     |

| Clear Flag 0      | CLR Fo   | 85   | 1    | 1     | _   | _  | Z  | _  | $0 \rightarrow (F_0)$                |

| Complement Flag 0 | CPL F    | 95   | 1    | 1     |     | _  | CP | _  | $(\overline{F_0}) \rightarrow (F_0)$ |

| Clear Flag 1      | CLR F    | A5   | 1    | 1     | _   | _  | _  | Z  | $0 \rightarrow (F_1)$                |

| Complement Flag 1 | CPL F    | B5   | 1    | 1     | _   | _  | _  | CP | $(\overline{F_1}) \to (F_1)$         |

Operation Code X: Tables-1, 2 %: Table 3

Flag\*: This flag is set or reset in the state after executed instruction.

Z: This flag is reset.

CP: This flag is complemented.

- The accumulator value is adjusted to form BCD digits following the binary addition of BCD numbers.

- 2) DJNZ  $R_r$ , addr;  $(R_r) 1 \rightarrow (R_r)$ if  $(R_r) \neq 0$  addr  $\rightarrow (PC_0 \text{ to } PC_7)$ if  $(R_r) = 0$  execute next instruction

- 3) JMPP @A ((A)) → (PC<sub>0</sub> to PC<sub>7</sub>)

- 4) CALL addr CALL addr  $(PC_0 \text{ to } PC_7) - ((SP))$  (SP) + 1 - (SP) (SP) + 1 - (SP)  $(PC_8 \text{ to } PC_{11})$ , (MBF),  $(PSW_4 \text{ to } PSW_7) - ((SP))$  (SP) + 1 - (SP)  $A_L - (PC_0 \text{ to } PC_7)$   $A_H - (PC_8 \text{ to } PC_{10})$   $MBF - (PC_{11})$

- 5) RET  $\begin{array}{l} \text{RE1} \\ (\text{SP}) - 1 \rightarrow (\text{SP}) \\ ((\text{SP})_0 \text{ to } (\text{SP})_3) \rightarrow ((\text{PC})_8 \text{ to } (\text{PC})_{11}) \\ (\text{SP}) - 1 \rightarrow (\text{SP}) \\ ((\text{SP})) \rightarrow (\text{PC}_0 \text{ to } \text{PC}_7) \end{array}$

- 6) RETR RETR

(SP) = 1 -- (SP)

((SP)<sub>0</sub> to (SP)<sub>3</sub>) -- (PC<sub>6</sub> to PC<sub>11</sub>)

((SP)<sub>4</sub> to (SP)<sub>7</sub>) -- (PSW<sub>4</sub> to PSW<sub>7</sub>)

(SP) - 1 -- (SP)

((SP)) -- (PC<sub>6</sub> to PC<sub>7</sub>) A<sub>L</sub>: Lower B Bits of Address A<sub>H</sub>: A<sub>8</sub>, A<sub>9</sub>, A<sub>10</sub> of Address MBF: Memory Bank Flag

### **Instruction Set Summary**

(Continued)

#### OP Code of Register Access (Table 1)

| Mnemonic     | Rr | RO | R1 | R2         | R3 | R4 | R5 | R6 | R7 |

|--------------|----|----|----|------------|----|----|----|----|----|

| INC Rr       |    | 18 | 19 | 1A         | 1B | 1C | 1D | 1E | 1F |

| XCH A,Rr     |    | 28 | 29 | 2A         | 2B | 2C | 2D | 2E | 2F |

| ORL A, Rr    |    | 48 | 49 | 4A         | 4B | 4C | 4D | 4E | 4F |

| ANL A,Rr     |    | 58 | 59 | 5 <b>A</b> | 5B | 5C | 5D | 5E | 5F |

| ADD A,Rr     |    | 68 | 69 | 6A         | 6B | 6C | 6D | 6E | 6F |

| ADDC A,Rr    |    | 78 | 79 | 7A         | 7B | 7C | 7D | 7E | 7F |

| MOV Rr,A     |    | Α8 | Α9 | AA         | ΑB | AC | ΑĐ | ΑE | AF |

| MOV Rr,#data |    | В8 | B9 | ВА         | вв | вс | BD | BE | BF |

| DEC Rr       |    | C8 | C9 | CA         | СВ | CC | CD | CE | CF |

| XRL A,Rr     |    | D8 | D9 | DA         | DB | DC | DD | DΕ | DF |

| DJNZ Rr,M    |    | E8 | E9 | EΑ         | ΕB | EC | ED | EΕ | EF |

| MOV A,Rr     |    | F8 | F9 | FA         | FB | FC | FD | FE | FF |

| 7 | 6 | 5 | 4 | 3 | 2              | 1              | 0  |

|---|---|---|---|---|----------------|----------------|----|

|   |   |   |   |   | r <sub>2</sub> | r <sub>1</sub> | ro |

### OP Code of Expander (Table 2)

| Mnemonic               | PP | P4 | P5 | P6 | P7 |  |

|------------------------|----|----|----|----|----|--|

| MOVD A,P <sub>P</sub>  |    | 0C | 0D | 0E | 0F |  |

| MOVD P <sub>P</sub> ,A |    | 3C | 3D | 3E | 3F |  |

| ORLD P <sub>P</sub> ,A |    | 8C | ab | 8E | 8F |  |

| ANLD P <sub>P</sub> .A |    | 9C | 9D | 9€ | 9F |  |

| 7 | 6 | 5 | 4 | 3 | 2 | 1              | 0     |

|---|---|---|---|---|---|----------------|-------|

|   |   |   |   |   |   | P <sub>1</sub> | $P_0$ |

#### OP Code of JMP, CALL, JB, (Table 3)

#### Instruction Codes

| H L | 0             | 1             | 2             | 3             | 4             | 5            | 6            | 7            | 8            | 9            | A            | В            | С            | D            | E            | f            |

|-----|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 0   | NOP           | HALT          | OUTL<br>BSU.A | ADD<br>A.#    | JMP<br>0××    | EN<br>1      |              | DEC<br>A     | INS<br>A,BUS | IN<br>A.P1   | IN<br>A.P2   |              | MOVD<br>A,P4 | MOVD<br>A,P5 | MOVD<br>A,P6 | MOVD<br>A,P7 |

| 1   | INC<br>@R0    | INC<br>@R1    | JB0<br>addr   | ADDC<br>A#    | CALL<br>0 x x | DIS<br>1     | JTF<br>addr  | INC<br>A     | INC<br>R0    | INC<br>R1    | INC<br>F2    | INC<br>R0    | INC<br>R4    | INC<br>R5    | INC<br>R6    | INC<br>R7    |

| 2   | XCH<br>A,@R0  | XCH<br>A,@R1  |               | MOV<br>A.#    | JMP<br>1 x x  | EN<br>TCNT1  | JNT0<br>addr | CLR<br>A     | XCH<br>A.R0  | XCH<br>A,R1  | XCH<br>A,R2  | XCH<br>A,R3  | XCH<br>A.R4  | XCH<br>A.R5  | XCH<br>A.R6  | XCH<br>A.R7  |

| 3   | XCHD<br>A.@R0 | XCHD<br>A.@R1 | JB1<br>addr   |               | CALL<br>1 x x | DIS<br>TCNT1 | JT0<br>addr  | CPL<br>A     |              | OUTL<br>P1.A | OUTL<br>P2,A |              | MOVD<br>P4,A | MOVD<br>P5,A | MOVD<br>P6.A | MOVD<br>P7,A |

| 4   | ORL<br>A.@R0  | ORL<br>A.@R1  | MOV<br>A.T    | ORL<br>A,#    | JMP<br>2 x x  | STRT         | JNT1<br>addr | SWAP<br>A    | ORL<br>A.R0  | ORL<br>A,R1  | ORL<br>A,R2  | ORL<br>A.R3  | ORL<br>A,R4  | ORL<br>A.R5  | ORL<br>A,R6  | ORL<br>A,R7  |

| 5   | ANL<br>A.@R0  | ANL<br>A.@R1  | JB2<br>addr   | ANL<br>A.#    | CALL<br>2 x x | STRT         | JT1<br>addr  | DA<br>A      | ANL<br>A,R0  | ANL<br>A,R1  | ANL<br>A,R2  | ANL<br>A.R3  | ANL<br>A.R4  | ANL<br>A.R5  | ANL<br>A,R6  | ANL<br>A.R7  |

| 6   | ADD<br>A.@R0  | ADD<br>A.@R1  | MOV<br>T,A    |               | JMP<br>3 x x  | STOP<br>TCNT |              | RRC<br>A     | ADĐ<br>A,R0  | ADD<br>A.R1  | ADD<br>A.R2  | ADD<br>A.R3  | ADD<br>A,R4  | ADD<br>A.R5  | ADD<br>A.R6  | ADD<br>A,R7  |

| 7   | ADDC<br>A,@R0 | ADDC<br>A.@R1 | JB3<br>addr   |               | CALL<br>3 x x | ENTO<br>CLK  | JF1<br>addr  | RR<br>A      | ADDC<br>A,R0 | ADDC<br>A,R1 | ADDC<br>A,R2 | ADDC<br>A.R3 | ADDC<br>A,R4 | ADDC<br>A.R5 | ADDC<br>A,R6 | ADDC<br>A,R7 |

| 8   | MOVX<br>A,@R0 | MOVX<br>A.@R1 |               | RET           | JMP<br>4××    | CLR<br>F0    | JN1<br>addr  |              | ORL<br>BUS.# | ORL<br>P1,#  | ORL<br>P2.#  |              | ORLD<br>P4,A | ORLD<br>P5,A | OALD<br>P6.A | ORLD<br>P7.A |

| 9   | MOVX<br>@R0.A | MOVX<br>@R1.A | JB4<br>addr   | RETR          | CALL<br>4 x x | CPL<br>F0    | JNZ<br>addr  | CLR<br>C     | ANL<br>BUS.# | ANL<br>P1. ≢ | ANL<br>P2. # |              | ANLD<br>P4,A | ANLD<br>P5,A | ANLD<br>P6,A | ANLD<br>P7,A |

| A   | MOV<br>@R0,A  | MOV<br>@R1.A  |               | MOVP<br>A.@A  | JMP<br>5 × ×  | CLR<br>F1    |              | CPL<br>C     | MOV<br>Ro,A  | MOV<br>R1.A  | MOV<br>R2.A  | MOV<br>R3.A  | MOV<br>R4,A  | MOV<br>R5.A  | MOV<br>R6,A  | MOV<br>R7,A  |

| В   | MOV<br>@R0.#  | MOV<br>@R1,#  | JB5<br>addr   | JMPP<br>@A    | CALL<br>5 × × | CPL<br>F1    | JF0<br>addr  |              | MOV<br>R0#   | MOV<br>R1#   | MOV<br>R2#   | MOV<br>R3#   | MOV<br>R4#   | MOV<br>R5#   | MOV<br>R6#   | MOV<br>R7#   |

| С   |               |               |               |               | JMP<br>6×x    | SEL<br>RB0   | JZ<br>addr   | MOV<br>A.PSW | DEC<br>R0    | DEC<br>R1    | DEC<br>R2    | DEC<br>R3    | DEC<br>R4    | DEC<br>R5    | DEC<br>R6    | DEC<br>R7    |

| D   | XRL<br>A,@R0  | XRL<br>A.@R1  | JB6<br>addr   | XRL<br>A#     | CALL<br>6 x x | SEL<br>RB1   |              | MOV<br>PSW,A | XRL<br>A.R0  | XRL<br>A,R1  | XRL<br>A.R2  | XRL<br>A.R3  | XRL<br>A,R4  | XRL<br>A,R5  | XRL<br>A,R6  | XRL<br>A,R7  |

| E   |               |               |               | MOVP3<br>A.@A | JMP<br>7 x x  | SEL<br>MB0   | JNC<br>addr  | RL<br>A      | DJNZ<br>R0,M | DJNZ<br>R1,M | DJNZ<br>R2.M | DJNZ<br>R3.M | DJNZ<br>R4,M | DJNZ<br>R5.M | DJNZ<br>R6,M | DJNZ<br>R7,M |

| F   | MOV<br>A.@R0  | MOV<br>A,@R1  | JB7<br>addr   |               | CALL<br>7 x x | SEL<br>MB1   | JC<br>addr   | RLC<br>A     | MOV<br>A,R0  | MOV<br>A.R1  | MOV<br>A.R2  | MOV<br>A.R3  | MOV<br>A,R4  | MOV<br>A.R5  | MOV<br>A.R6  | MOV<br>A,R7  |

#: Immediate data H; Higher 4 bits L; Lower 4 bits Single-byte, Single-cycle Instruction

Single-byte, Two-cycle Instruction

Two-byte, Two-cycle Instruction

## Typical Applications

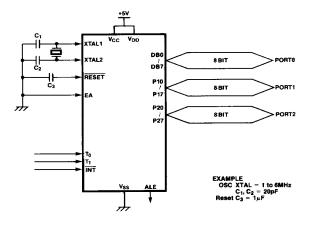

#### (1) Stand Alone System

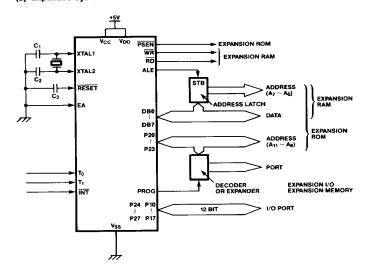

#### (2) Expanded System

#### Absolute Maximum Ratings†

| Parameter             | Symbol                            | Value        | Unit |

|-----------------------|-----------------------------------|--------------|------|

| Supply Voltage        | V <sub>CC</sub> , V <sub>DD</sub> | -0.3 to +7.0 | ٧    |

| Input Voltage         | V <sub>IN</sub>                   | -0.3 to +7.0 | ٧    |

| Operating Temperature | T <sub>A</sub>                    | 0 to +70     | °C   |

| Storage Temperature   | T <sub>stg</sub>                  | -55 to +150  | °C   |

| Power Dissipation     | P <sub>D</sub>                    | 1.5          | w    |

†Permanent device damage may occur if the ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Recommended Operating Conditions

| Parameter             | Symbol                            | Value     | Unit |  |

|-----------------------|-----------------------------------|-----------|------|--|

| upply Voltage         | V <sub>CC</sub> , V <sub>DD</sub> | +5.0 ±10% | ٧    |  |

| Supply Voltage        | V <sub>SS</sub>                   | 0         | ٧    |  |

| Operating Temperature | TA                                | 0 to +70  | °C   |  |

DC Characteristics  $(T_A = 0$ °C to +70°C,  $V_{CC} = V_{DD}$  = 5.0V  $\pm 10$ %,  $V_{SS} = 0$ V)

|                                |                                          |                  | Test                                                          | Value |                 |      |

|--------------------------------|------------------------------------------|------------------|---------------------------------------------------------------|-------|-----------------|------|

| Parameter                      |                                          | Symbol           | Conditions                                                    | Min.  | Max.            | Unit |

| Input Low Voltage              | All Except XTAL1, 2, RESET               | V <sub>IL</sub>  |                                                               | -0.3  | 8.0             | ٧    |

|                                | XTAL1,2, RESET                           | V <sub>IL1</sub> |                                                               | -0.3  | 0.6             | ٧    |

| Input High Voltage             | All Except XTAL1, 2, RESET               | V <sub>IH</sub>  |                                                               | 2.0   | $v_{cc}$        | ٧    |

|                                | XTAL1,2, RESET                           | V <sub>IH1</sub> |                                                               | 3.8   | V <sub>CC</sub> | ٧    |

| Andrew Value VI                | BUS                                      | V <sub>OL</sub>  | I <sub>OL</sub> = 2.0mA                                       |       | 0.45            | ٧    |

| Output Low Voltage             | RD, WR, PSEN, ALE                        | V <sub>OL1</sub> | I <sub>OL</sub> = 2.0mA                                       |       | 0.45            | ٧    |

| Output Low vortage             | PROG                                     | V <sub>OL2</sub> | I <sub>OL</sub> = 1.0mA                                       |       | 0.45            | ٧    |

|                                | Other outputs                            | V <sub>OL3</sub> | I <sub>OL</sub> = 1.6mA                                       |       | 0.45            | V    |

|                                | BUS                                      | V <sub>OH</sub>  | I <sub>OH</sub> = -400μA                                      | 2.4   |                 | ٧    |

| Output High Voltage            | RD, WR, PSEN, ALE                        |                  | I <sub>OH</sub> = -100μA                                      | 2.4   |                 | ٧    |

|                                | Other Outputs                            | V <sub>OH2</sub> | I <sub>OH</sub> = -50μA                                       | 2.4   |                 | V    |

| Innut Lookogo                  | T <sub>1</sub> , INT                     | I <sub>IL</sub>  | V <sub>SS</sub> $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> |       | ±10             | μΑ   |

| Input Leakage<br>Current       | P10 <u>-P1</u> 7, P20-P27<br>EA, SS      | I <sub>IL1</sub> | $V_{SS}$ + 0.45V $\leq$ $V_{IN} \leq$ $V_{CC}$                |       | -500            | μΑ   |

| Output Leakage<br>Current      | BUS, T <sub>0</sub> (High-<br>Impedance) | loL              | $V_{SS} + 0.45V \le V_{IN} \le V_{CC}$                        |       | ±10             | μΑ   |

| V                              | MBL8049/39N/E                            | 1                |                                                               |       | 30              | mA   |

| V <sub>DD</sub> Supply Current | MBL8049/39H                              | IDD              |                                                               |       | 50              | mA   |

| T-4-1 C 1 . C                  | MBL8049/39N/E                            | 1 11             |                                                               |       | 150             | mA   |

| Total Supply Current           | MBL8049/39H                              | IDD + ICC        |                                                               |       | 170             | mA   |

AC Characteristics\*

(T<sub>A</sub> = 0°C to +70°C, V<sub>CC</sub> = V<sub>DD</sub>

= 5.0V ±10%, V<sub>SS</sub> = 0V

|                                                        |                    | H-Ve | rsion | E-Ver | sion | N-Version |      |      |

|--------------------------------------------------------|--------------------|------|-------|-------|------|-----------|------|------|

| Parameter                                              | Symbol             | Min. | Max.  | Min.  | Max. | Min.      | Max. | Unit |

| ALE Pulse Width                                        | t <sub>LL</sub>    | 150  |       | 260   |      | 410       |      | ns   |

| Address Setup Time (to ALEI)                           | t <sub>AL</sub>    | 70   |       | 140   |      | 230       |      | ns   |

| Address Hold Time (from ALE+)                          | t <sub>LA</sub>    | 50   |       | 80    |      | 120       |      | ns   |

| Control Pulse Width (RD, WR)                           | t <sub>CC1</sub>   | 480  |       | 730   |      | 1050      |      | ns   |

| Control Pulse Width (PSEN)                             | t <sub>CC2</sub>   | 350  |       | 550   |      | 800       |      | ns   |

| Data Setup Time (before WRI)                           | t <sub>DW</sub>    | 390  |       | 610   |      | 880       |      | ns   |

| Data Hold Time (after WR1)**                           | t <sub>WD</sub>    | 40   |       | 80    |      | 120       |      | ns   |

| Data Hold Time<br>(after RDt, PSENt)                   | t <sub>DR</sub>    | 0    | 110   | 0     | 160  | 0         | 220  | ns   |

| Data Delayed Time<br>(RDI to data in)                  | t <sub>RD1</sub>   |      | 350   |       | 550  |           | 800  | ns   |

| Data Delayed Time<br>(PSENI to data in)                | t <sub>RD2</sub>   |      | 210   |       | 360  |           | 550  | ns   |

| Address Setup Time (to WRI)                            | t <sub>AW</sub>    | 310  |       | 480   |      | 680       |      | ns   |

| Address Setup Time (RD, to data in)                    | t <sub>AD1</sub>   |      | 760   |       | 1130 |           | 1590 | ns   |

| Address Setup Time (PSEN, to data in)                  | t <sub>AD2</sub>   |      | 480   |       | 750  |           | 1090 | ns   |

| Address Floating Time (to RDI, WRI)                    | t <sub>AFC1</sub>  | 140  |       | 210   |      | 290       |      | ns   |

| Address Floating Time (to PSEN <sub>1</sub> )          | t <sub>AFC2</sub>  | 10   |       | 20    |      | 40        |      | ns   |

| RD, WR Output Time (from ALEI)                         | t <sub>LAFC1</sub> | 200  |       | 300   |      | 420       |      | ns   |

| PSEN Output Time (from ALEI)                           | t <sub>LAFC2</sub> | 60   |       | 110   |      | 170       |      | ns   |

| ALE Output Time<br>(from RD1, WR1, PROG1)              | t <sub>CA1</sub>   | 50   |       | 80    |      | 120       |      | ns   |

| ALE Output Time (from PSEN1)                           | t <sub>CA2</sub>   | 320  |       | 460   |      | 620       |      | ns   |

| Port Control Setup Before<br>Falling Edge of PROG Time | t <sub>CP</sub>    | 100  |       | 170   |      | 250       |      | ns   |

| Port Control Hold After<br>Falling Edge of PROG Time   | t <sub>PC</sub>    | 160  |       | 300   |      | 460       |      | ns   |

| PROG Time P2 Input<br>Must Be Valid                    | t <sub>PR</sub>    |      | 700   |       | 1000 |           | 1380 | ns   |

| P2 Input Data Hold Time (after PROG1)                  | tpp                | 0    | 140   | 0     | 190  | 0         | 250  | ns   |

| Output Data Setup Time<br>(to PROG!)                   | t <sub>DP</sub>    | 400  |       | 600   |      | 850       |      | ns   |

| Output Data Hold Time (after PROG1)                    | t <sub>PD</sub>    | 90   |       | 130   |      | 200       |      | ns   |

| PROG Pulse Width                                       | tpp                | 700  |       | 1060  |      | 1500      |      | ns   |

| Port2 I/O Data Setup Time (to ALE1)                    | tpL                | 160  |       | 300   |      | 460       |      | ns   |

| Port2 I/O Data Hold Time (from ALE1)                   | t <sub>LP</sub>    | 40   |       | 60    |      | 80        |      | ns   |

| Port Data Output Time (from ALEI)                      | t <sub>PV</sub>    |      | 510   |       | 660  |           | 850  | ns   |

| Cycle Time***                                          | t <sub>CY</sub>    | 1.36 |       | 1.875 |      | 2.5       |      | μs   |

| T <sub>0</sub> Output Cycle Time                       | t <sub>OPRR</sub>  | 270  |       | 370   |      | 500       |      | ns   |

|                                                        |                    |      |       |       |      |           |      |      |

<sup>\*: 6</sup>MHz XTAL (N-Version), 8MHz XTAL (E-Version), 11MHz XTAL (H-Version) Load Conditions: BUS.  $C_L$  = 150pF; Other Outputs  $C_L$  = 80pF. \*\*: Load Conditions  $C_L$  = 20pF, High Impedance \*\*:  $t_{CY}$  = 2.5 $\mu$ s (6MHz XTAL N-Version),  $t_{CY}$  = 1.875 $\mu$ s (8MHz XTAL E-Version),  $t_{CY}$  = 1.36 $\mu$ s (11MHz XTAL H-Version)

#### **Timing Diagram**

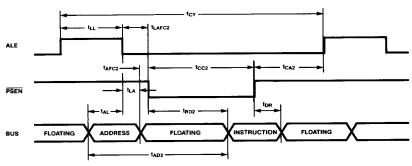

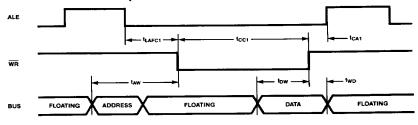

#### Instruction Fetch From External Program Memory

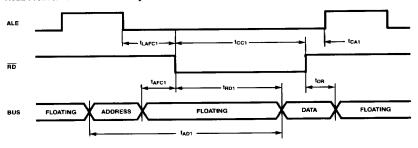

#### Read From External Data Memory

#### Write To External Data Memory

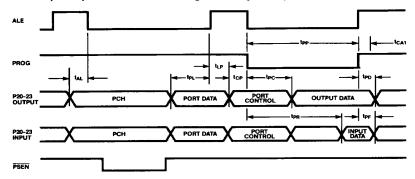

## Timing Diagram (Continued)

P20-23 Input/Output For Use Of External Program Memory And Expander I/O Port

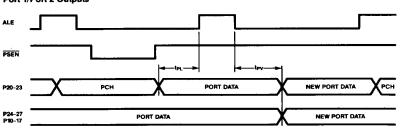

Port 1/Port 2 Outputs

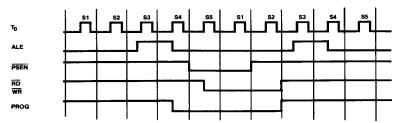

**Clock Outputs**

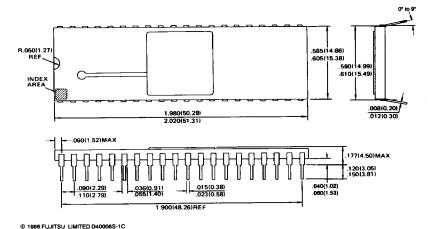

# Package Dimensions Dimensions in inches (millimeters)

40-Lead Ceramic (Metal Seal) Dual In-Line Package (Case No.: DIP-40C-A01)

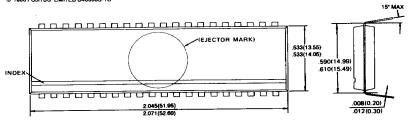

#### 40-Lead Plastic Dual In-Line Package (Case No.: DIP-40P-M01)

#### © 1985 FUJITSU LIMITED D40005S-1C

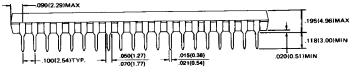

**Oscillation Circuits**

Crystal Oscillator

5V MBL8049 MBL8039 XTAL1

4700 SV XTAL1

4700 SV XTAL2

Including stray capacitances

\*Both high and low times should be more than 35% of the cycle time, and rise and fall times should be less than 20 ns.

External Clock Drive

2-41